- Introduction and general issues

- •Parallel bus communication (IEEE 488)

- •Serial bus communications (RS232 ... and USART driving)

- •Field bus (Fip, CanBus)

•Encoding = bijective correspondence between transmitted info and symbols

- •The encoding can be arbitrary but must be followed by both the communicating devices otherwise non comprehension

- •Symbols are sent through signals associated to values ranges (within the calculator) or subject to modulation (in the used medium)

- •Transmission media: wired twists and/or shielded, Wi-Fi (pay attention to the environmental disturbs), coaxial cables, optical fibers (pay attention to costs, maintenance, installation and required competences).

•Characteristics:

```

•bandwidth (100 KHz - 1 GHz)? max. transmission velocity

```

•attenuation (0.4-1.5 dB/Km)? max. distance without repeaters (e<sup>-? |</sup>)

propagation velocity (15000-150000 Km/s)

•characteristic impedance (50-100 Ohm)

•noise immunity (S/N, 100 dB)

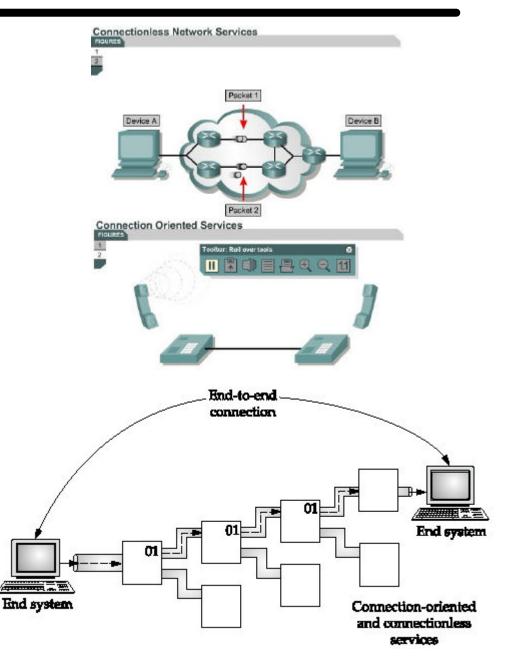

#### •THE GENERAL PROBLEMS OF THE DIGITAL COMMUNICATIONS

- -Transfer direction (simplex, half and full duplex)

- -Organize the transmission content (bits, characters and messages)

- -Data synchronization and recognition (auxiliary signals)

- -Error avoidance

- -Error recognition and correction

- -Spatial and temporal coordination of interlocutors through protocols (who can transmit and how) and routing (shortest vs most efficient path policies)

#### • TRANSFER DIRECTION

- simplex, only one single-direction channel that allows to transfer from a sender to many (multicast) or all (broadcast) destinations.

- half duplex: 1 bi-directional shared channel or 2 singledirection opposed channels of which only one can send or receive (for instance the walkie talkie). Simple approach typical in local networks.

- full duplex: transmission and reception can occur simultaneously on the same channel (for instance telephone). The communication can consist of 2 simplex opposed channels or of 1 bi-directional channel.

#### • TRANSMISSION CONTENT

- Hierarchical structure of information (bits, characters and messages)

- Characters are made up by bits (7, 8 or 9)

- ASCII or different format encoding to make the transmission content more compact and improve the robustness (immunity) to the noise

- Characters are organized in messages to

»Recover in a easier way the information content, by simplifying error detection and recognition

»Synchronize interlocutors

»Allow concurrent communications on the same transmission mean

Characters length influenced by the error management techniques (duplications and redundancy)

#### • SYNCHRONIZATION AND RECOGNITION

- Synchronization = to establish what time windows can be used to exchange information and what symbols are used to represent them

- Auxiliary signals

- If parallel communications ? one or more addictive lines

- If serial communications? data and synchronization info are brought by the same line (for instance in synchronous communication)

- Bit, characters and message structure ? synchronization signals must be organized in a similar structure to recognize those bits that constitute a character and the bits that constitute a message (for instance in the asynchronous communication start and stop bits, SOM and EOM, ...)

#### • ERROR PREVENTION

- Disturbing phenomena restraint (filtering, differential amplification with high CMRR)

- Preventing from disturbs (shielding, sheaths, twisted pairs)

- "Robust" signals (high S/N)

#### • ERROR RECOGNITION AND CORRECTION

- Errors can never completely eliminated ? error rate ?0 that must be accepted and foreseen in the specs

- Errors rate can be even high but it is important that errors are detected and when possible original data recreated

»Not detected errors (if possible with a low rate)

»Detected errors with relative information discarding

»Recognized errors with information recovery

### • PARALLEL COMMUNICATIONS

- Groups of bits simultaneously transmitted

- Short distances (mechanical use and disturbs)

- System bus (with separated data and addresses) vs communication bus (data and addresses together)

- Auxiliary signals to synchronize the transfers (asynchronous bus). For instance:

- » ReadReq (memory read requirement? the address is put on the bus)

- » DataRdy (the data are ready and on the bus: the signal is managed by the sender)

- » Ack (ok reception of ReadReq and DataRdy and of the data)

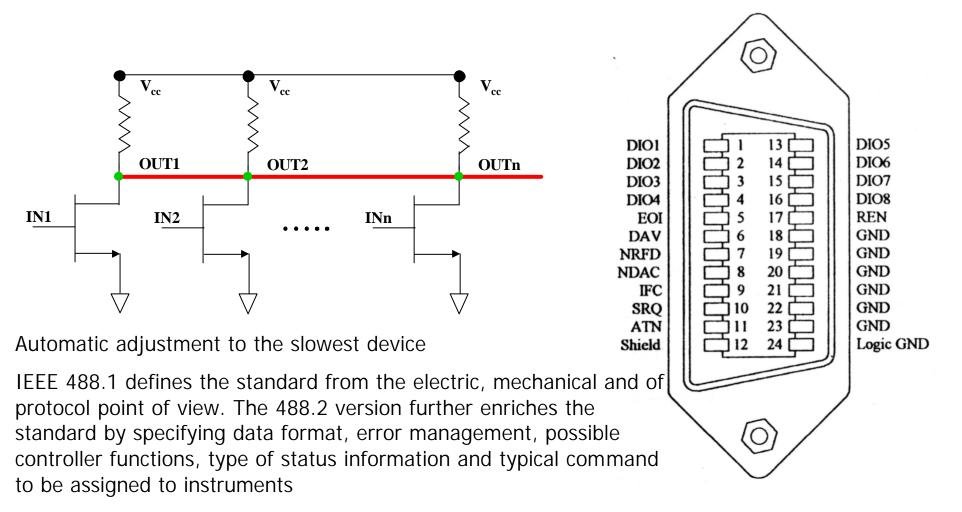

- Existent standards for interfacing: IEEE 488 and Centronics

•OBSERVATION: why do not use synchronous buses?

In a synchronous bus the clock signal is included in the control lines

The use of a synchronous bus requires a fixed protocol for the communication that is a sequence of steps executed at a certain clock cycle (CC) sequence

For instance: in the first CC a "read" command and the relative address are sent by a device to the memory. The memory after few cycles (for example 5) provides the requested data on the bus, then the device reads in three CC and elaborates...

This can be implemented with a small finite state machine ? very few digital logic required, very fast response and small interfacing, but ...

... all the devices must work at the same frequency (this is not said)

... the buses *must* be kept physically short to avoid the misalignment with respect other devices (*clock skew*)

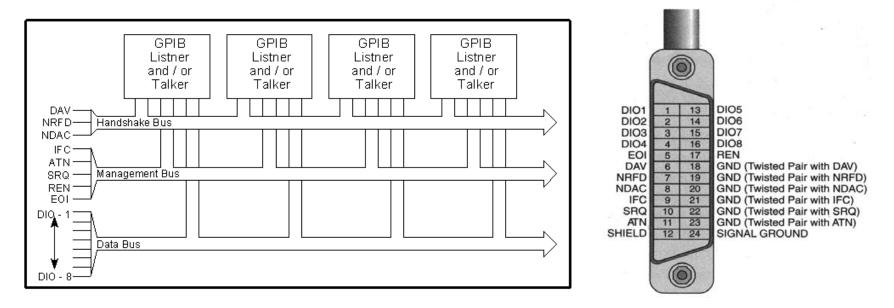

#### •PARALLEL COMMUNICATIONS: IEEE 488 STANDARD BUS

**GPIB = General Purpose Interface Bus**

At the beginning ('75) proposed by HP to carry out a network between calculation systems and instrumentations by different manufacturers (named HPIB)

Successively it was adopted as a standard by IEEE and redefined

The standard allows to connect up to 15 devices on the same bus

16 lines of which 8 of data, 3 for the *handshake* and 5 for interfacing management

The devices can play 3 possible roles: "*talker*", "*listener*" and "*controller*": thus it is possible to specify type and functions of the connected instrumentation

A device is programmed to be the System Controller at the beginning or the Active Controller during the normal working cycle and among its main functions can send a reset (IFC - interface clear) to all the devices or enable them to transmit (REN – remote enable)

**Transmission velocity = MB/sec**

Max. length of the bus 20 m; max. distance between devices 4 m.

University of Pavia - Francesco Leporati - Industrial Informatics and Embedded Systems 17

#### • PARALLEL COMUNICATIONS: IEEE 488 STANDARD BUS

- •Several "controllers" can be present ma only 1 at a time will be active (In Charge)

- •The control is passed among the "active controllers" through a token mechanism (only the System Controller is established on the basis of the given system configuration)

- •A "listener" device receives data from the bus only when the "controller" enables it

- •Similarly a "talker" device transmits only when enabled

- •The "controller" can set a "multicast" transmission mode between a "talker" device and a "listeners" group

University of Pavia - Francesco Leporati - Industrial Informatics and Embedded Systems 17

•ATN (attention) is asserted by the "Controller" to indicate the placement of an address/control on the bus. The "Controller" disables it to allow the "talker" to transmit then re-enables it to continue in the transmission management

•EOI (end or identify) two possible uses: if enabled by the "talker" it means end of transmission; if enabled by the "controller", together with it ATN, it stands for a (parallel poll) to all the devices

- IFC (Interface Clear) enabled only by the "System Controller" to bring all the devices in a known initial state

- •REN (Remote Enable) enabled only by the "System Controller" to arrange the devices in a remote control mode (command reception) that disables the local control from front panel (if present). The control will become complete only when those devices will be addressed as "listener"

•SRQ (Service Request) = a kind of interrupt by a whatever device that asks the "Controller" for a certain action. The "Controller" identifies the emitting device through a "serial poll". When polled, the device releases the SRQ signal University of Pavia - Francesco Leporati - Industrial Informatics and Embedded Systems 17

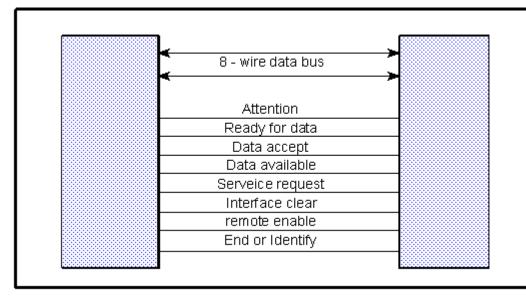

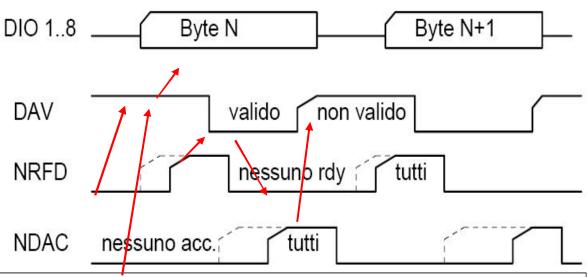

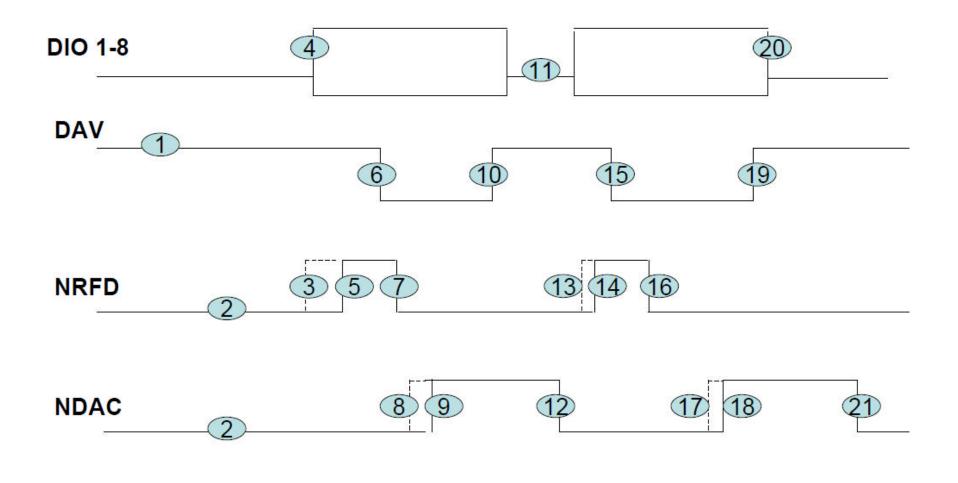

•IEEE 488: handshake signals D

TTL inverse logic signals

NRFD (Not Ready For Data): setDAhigh from receivers (low active)if ready to accept data. Openollector

#### DIO: data lines

DAV (Data Valid): active low only after the data have been put on the bus and the NRFD signal has been found high

NDAC (Not Data Accepted): set low by receivers until a new byte has not been acquired. If high, DAV will be disabled and DIO lines changed with a new value. Open collector

#### Handshake

- 1. DAV high if the sender ("controller"/"talker") wants to transmit. If NRFD and NDAC low, data are written in the bus DIO. Only when NRFD high, DAV will be set low by the sender

- 2. Every receiver keeps NRFD low to signal to be "busy"; when the last one will have complete the reception, NDAC will be set high and the sender will set DAV high to transmit the next byte.

- 3. If, when set high DAV, the sender finds NDAC and NRFD high an error happens. Moreover if a device cannot perform correctly the handshake and releases the NDAC or the NRFD a error happens.

4. The error is managed by the operative system as a time-out error

University of Pavia - Francesco Leporati - Industrial Informatics and Embedded Systems 17

Courtesy prof. Laracca – università di Cassino

#### •DEVICE ADDRESSING (when ATN true)

The 5 low bits constitute a primary address (MSb always 0, parity check)

Bit 5 indicates Listener address

Bit 6 indicates Talker address

UNT = Disable talkers = 3F; UNL = Disable listeners = BF

A secondary address can be conceived to address sub-units of a generic device. Normal addressing followed by a secondary address with bit 5-6 set to 11

#### Commands

The following commands control the bus operations and can be grouped in 4 classes: *Universal (Multiline, to all the peripherals with handshake):* DCL, LLO, SPE, SPD, PPU, UNT, UNL *Uniline (to all periph. without handshake):* IFC (Interf. Clear), REN (Remote En.), ATN (Attent.) *Addressed:* GET, SDC, GTL, PPL, TCT *Secondary:* PPE, PPD

| Multiline Command            | Mnemonic | Action                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device Clear                 | DCL      | All the instruments are brought in a predefined state by the manufacturer, that depend on the instrument and specified in the datasheet; the device must be in remote mode or previously addressed.                                                                                                                                                                            |

| Local<br>Lockout             | LLO      | Disable the control "return-to-local" for the device (in practice disable<br>the instrument front panel). The device can be addressed in local or<br>remote mode. To enable again the local "return-to-local" control the<br>physical line REN must be brought to the logic value 0: in such a way<br>the device is set for local controlling (enabling from the front panel). |

| Serial Poll<br>Enable        | SPE      | A Serial Polling of all the devices that can be addressed as Talker is done; each one provides a status-byte, that represents with a suitable encoding the situation (service request, available data, errors,). Used to debug.                                                                                                                                                |

| Serial Poll<br>Disable       | SPD      | Terminates the Serial Poll mode while resets the devices in Talker mode, so they provide device-dependent information or other status generic information.                                                                                                                                                                                                                     |

| Parallel Poll<br>Unconfigure | PPU      | Terminates the peripheral parallel poll for diagnostic that is similar to the serial one but faster (each peripheral returns 1 bit) although with less information                                                                                                                                                                                                             |

| Untalk                       | UNT      | Disable the current Talker device. A similar result can be obtained by selecting another device as Talker.                                                                                                                                                                                                                                                                     |

| Unlisten                     | UNL      | Disable all the Listener devices since it is not possible to disable a single Listener; this command can be conveniently employed to disable all the listener devices, before enabling all those devices that we want to set as listener.                                                                                                                                      |

University of Pavia - Francesco Leporati - Industrial Informatics and Embedded Systems 17

| Addressed Command       | Mnemonic | Action                                                                                                                                                                                           |

|-------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Group Execute Trigger   | GET      | All the Listener devices receive the commend to start the action<br>previously defined for each of them. The GET command allows to<br>simultaneously synchronize many devices.                   |

| Selected Device Clear   | SDC      | All the devices addressed as Listener are brought back to a device-dependent pre-defined state. It is equivalent to the DCL command after the destination has been addressed                     |

| Go To Local             | GTL      | All the devices addressed as Listener are brought back in local control mode (exit from remote mode). The device will come back to the remote function if addressed as Listener with REN line 1. |

| Parallel Poll Configure | PPC      | All the devices addressed as Listener are configured as the command following PPC, waiting for a parallel poll.                                                                                  |

| Take Control Talker     | тст      | The "controller in charge" enable the current Talker device so as it assumes the role of Bus (Active) controller.                                                                                |

| Secondary Command     | Mnemonic | Action                                                                                                                                                                       |

|-----------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parallel Poll Enable  | PPE      | Configures all the devices that received the PPC command so as<br>they can answer to the Parallel Poll on a particular data line (DIO),<br>with a certain pre-defined value. |

| Parallel Poll Disable | PPD      | Disable the devices that received the PPC command so as they do not answer to the Parallel Poll (end of Parallel Poll).                                                      |

#### **Serial Polling**

A service request (SRQ) allows to the controller to receive info on the device state, but it allows also to the controller to understand if one or more devices asks for service.

Procedure: the ATN signal is activated (bus in command mode), the command SPE is sent, all the devices are sequentially checked, each of them returns its status byte, then the command SPD is sent eventually together with UNT.

#### **Parallel Polling**

The same as before concerning the status of a device. The Controller activates ATN, then sends the PPC command to each device, assigns to each one an I/O line for answering through the PPE command and sends a EOI (data request). Then it reads lines so identifying the device that requests the service and asks for a status byte to understand the requirement to fulfill.

Sometimes shared lines to provide logic AND/OR of the status of the sharing devices

The answer from a device must arrive within 200 nsec. The controller must read this answer within 2 ?sec after the 200 nsec.

Eventual disable with con PPD and end with PPU

#### SERIAL POLL

#### Advantages:

The controller achieves more information on the interrupt generation cause.

#### Drawbacks:

The time for a poll cycle augments with the number of connected devices.

#### PARALLEL POLL

#### Advantages :

The controller can poll up to 8 devices at the same time.

#### Drawbacks:

The status byte must be read to identify the interrupt cause.

Up to 8 devices can be parallel polled.

• PARALLEL COMMUNICATIONS: collector wired or connection

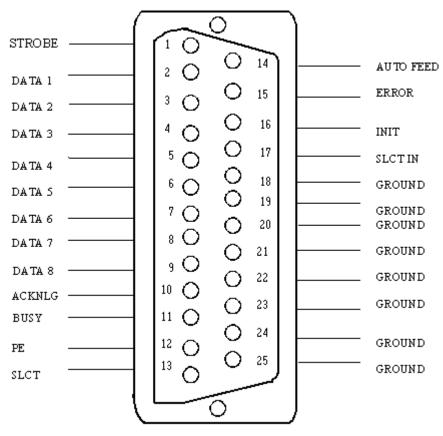

#### • PARALLEL COMMUNICATIONS : Centronics interface

- Standard interfacing between PC and old printers

- •8 data lines and 9 control ones

- •Output towards PC on a Cannon 25 poles jack

- •Bi-directional half-duplex connection

#### •SERIAL COMMUNICATIONS

A single signal bringing a sequence of bits one at a time

Short distances but more than parallel communications (up to hundreds of meters)

Transmission velocity expressed in symbol or bit per second (baud rate):

75?600 low standard velocities no more used

1200?9600 low standard velocities still used (PLC, ?P)

19200?56400 average standard velocities

100?1000 Kbit/sec average standard velocities for field bus

10?1000 Mbit/sec high velocities for local LAN

Characterizing issues:

bit, character, message synchronization techniques signal values, codification and eventual modulation error management

Existent standards: RS232 standard and successive versions and USB

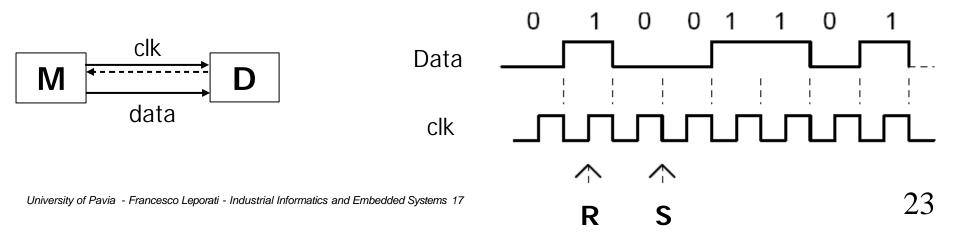

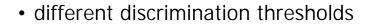

#### •SERIAL COMMUNICATIONS: bit synchronization

In what "time window" the receiver can sample and thus can read the voltage levels of the received signal

3 techniques: isochronous, asynchronous (mainly used with different manufacturers equipments) and synchronous (especially in field buses and local networks)

#### THE ISOCHRONOUS TECHNIQUE

A single clock signal shared between sender and recipients

The commutation edge on which the sender writes data is established conventionally (for instance falling edge) of course on the other edge the recipient will sample the line

#### •SERIAL COMMUNICATIONS: THE ISOCHRONOUS TECHNIQUE

Synchronization characters are used

Precision in the pulses duration not required (edges determine the sample time)

If clock is generated by sender clock and data are in phase since they travel together

If clock is generated by the recipient it is not in phase with data. The recipient will receive data with a delay twice the time needed to propagate the clock toward the sender and then back? the clock should be sized at lest = to this time.

Limitations in velocity ? short connections (also to avoid to collect noise)

RS232 mode a typical example

In another version a unique conditioned clock is used:

- ∠ a open collector signal between sender and recipient

- ✓ the recipient keeps the signal low until not ready, then it raises up

- $\varkappa$  when the sender detects the signal high starts to transmit and keeps low the signal

∠ Philips I<sup>2</sup>C bus

University of Pavia - Francesco Leporati - Industrial Informatics and Embedded Systems 17

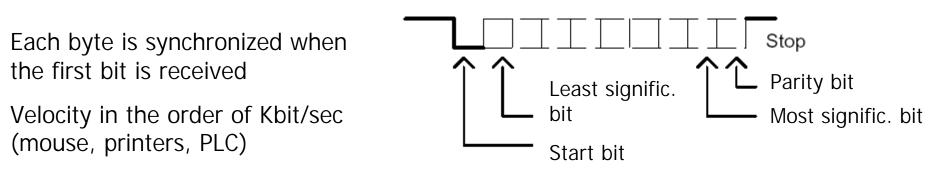

#### •SERIAL COMMUNICATIONS: THE ASYNCHRONOUS TECHNIQUE

Sender and recipient with their own independent clock regardless one or the other Similar stable clocks (tolerance 1...3%) with standard values (300, 600, 1200, 2400, 4800, 9600Hz)

Byte synchronization through start (0) and stop (1) bits with duration 1, 1.5, 2 bit

Message synchronization through silence intervals (1) between a character and the next Allowed phase shift ? half bit window time

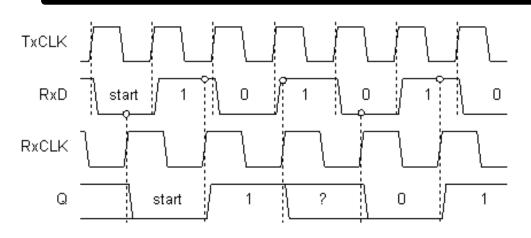

Asynchronous transmission with 8 bit datum and parity

TxCLK = sender internal clock used to synchronize serial data (RxD)

RxCLK = recipient internal clock, supposed slightly slower than TxCLK

**Q** = RxD bits as they arrive internally to the recipient

The two clocks feature a progressive phase shift that causes uncertainty on the value of the II bit (0) and the loss of the III bit (1). Conversely, if the sampling would be done very close to the beginning of each bit time window and if the sender clock frequency would be slightly minor than the recipient's one, the recipient could sample the same bit twice.

Therefore, the recipient clock must be re-synchronized at every start bit. The active edges (i. e. raising) will be located as much as possible in the center of the window time, so as to sample the RxD line as far as possible from those times into which the commutation can happen. This allows to tolerate slight differences between sender and recipient clocks.

The acceptable phase shift on 10 bit (8 data + start and stop) = ? 5%. This value diminishes when the edges cannot be considered as instantaneous (high velocities and limitation in the band.

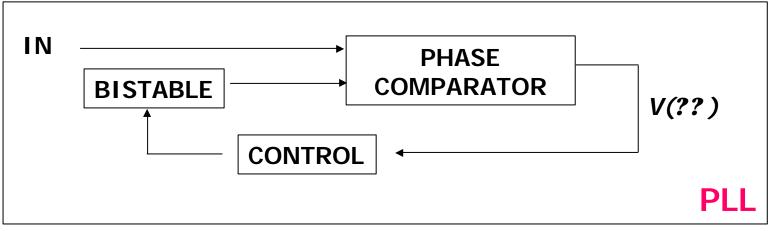

#### •SERIAL COMMUNICATIONS: THE SYNCHRONOUS TECHNIQUE

The sender features a free clock similar (but not equal) to the recipient: to cancel the phase shift a suitable PLL mechanism is provided PLL (phase lock loop)

Synchronization bits are transmitted at first (from 3 to 5)

Suitable characters must be chosen to favor the phase coupling (AAAA ko, A6A6 ok)

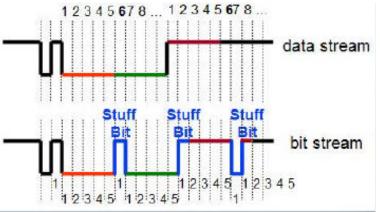

Avoid long "1s" or "0s" sequences that may vanish the phase coupling

More complexity but more efficiency (no start and stop bits) and velocities

The PLL mechanism compensates eventual jitters on the clock

University of Pavia - Francesco Leporati - Industrial Informatics and Embedded Systems 17

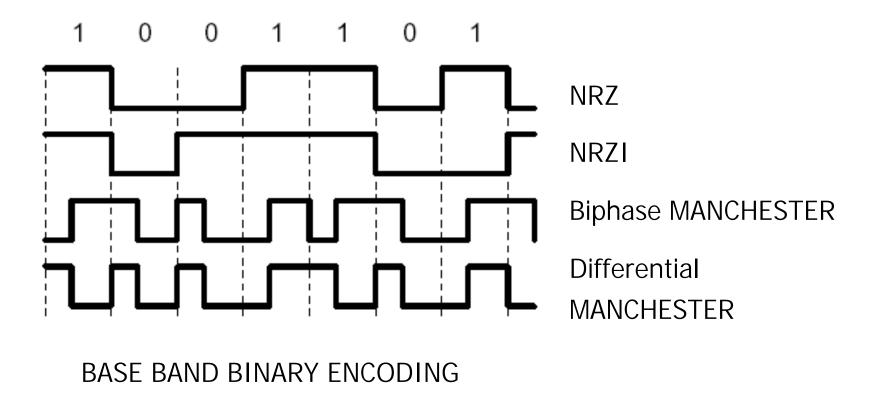

#### **BASE BAND ENCODING**

<u>NRZ (Not Reduced Zero)</u>: The signal level is kept constant throughout the bit time. It may cause synchronization problems if long sequences of equal bits should be sent.

?<u>*RZ* (*Reduced Zero*)</u>: The signal level is kept high only for a bit time fraction. Thus, the synchronization problems in case of long sequences of "1s" (high) is solved (but not in case of "0s" (low).

?<u>MANCHESTER</u>: The basic idea is to divide the bit time in two portions equally long. Each bit will be sent as the sequence of two NRZ coded bits each in half of the time window. I. e. the bit 1 is transmitted as a 0 bit and 1 bit while the bit 0 is transmitted as a 1 bit + a 0 bit. This halves the transmission efficiency that is per each bit to transmit, indeed two are sent. In practice a bandwidth is required twice as much as it would be necessary. It is pretty used in local Ethernet and Token-Ring networks.

?<u>NRZI (Non Reduced Zero Inverted</u>): It solves the long "1s" sequences problem. The value 0 is coded maintaining the signal level throughout the period. This level corresponds to the one of the last transmitted bit. On the other hand, the "1" causes a level transition (from low to high or vice-versa) compared to the value of the last transmitted bit. Conversely if the transition level is due to a "0" it solves the problem caused by the transmission of long sequences of "0s". Used in FDDI networks.

? *Differential MANCHESTER:* It joins Manchester with NRZI encoding.

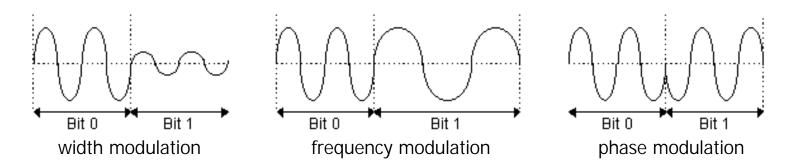

### •SINE SIGNALS ENCODING

Width, frequency, phase possible modulation

Used when communicating with modems on telephone lines, radio link or coaxial cables The "base band" signal is provided to the modem which carries out the modulation

#### •POSSIBLE SIGNAL RANGES

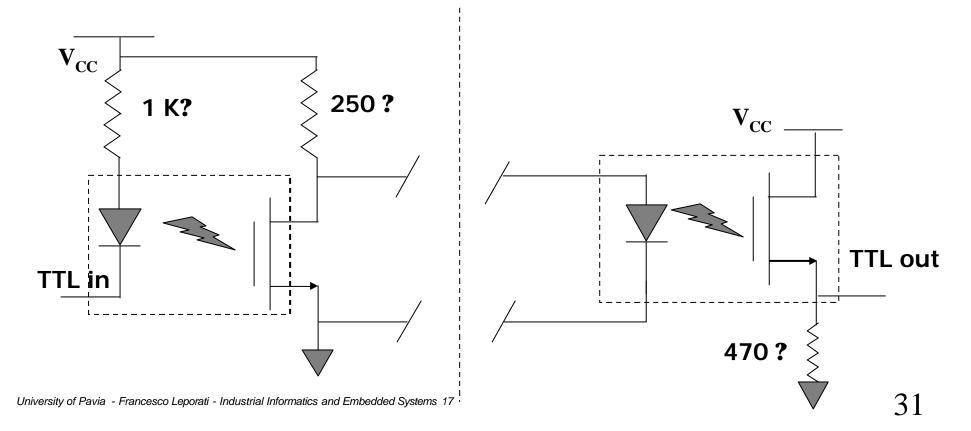

TTL level (0V ? 5V/3.3V)

bipolar voltages (-6V ? 6V): RS 232

Differential voltages: RS 485

"current loop" 0-20 mA

#### •Current loop 0-20 mA

low baud rates (2400)

High noise immunity, miles allowed length (ok for industrial environment)

The transmitted signal is current (20 mA) not voltage

#### • Errors

#### Recognition

- Error on a character: parity bits or autocorrecting Hamin code (corrects errors on M bits while recognizes them on N with N<M)</li>

- Errors on messages: additional characters are present made up by Cyclic Redundancy Check evaluated on 16 bits and sent as 2 characters or checksum or longitudinal parity

#### Correction

- Hamming codes and CRC require hw complexity (i. e. devoted circuits) and redundancy. Used only in critical applications

- Re-transmission

- The message length depends on the foreseen error rate: if a re-transmission is required also this one could be eventually affected by the error thus the problem will be not solved and the communication cost will be very high

University of Pavia - Francesco Leporati - Industrial Informatics and Embedded Systems 17

The Cyclic Redundancy Check associates bit streams to polynomial with 0 and 1 coefficients. A K bit string is read as a polynomial with K coefficients with degree  $\leq K-1$ . For instance:

110001 ->  $x^5 + x^4 + x^0$

The used arithmetic is *module 2*, without carries and borrows. Transmitter and receivers must agree on a G(X) common polynomial, said *generating polynomial*. The idea is to integrate the sequence with a suitable *checksum* making the final polynomial divisible byG(x). For instance:

- add r bit set to 0 to each bit frame so having a m+r bit sequence that corresponds to the polynomial x<sup>r</sup>× M(x), with r rank of G(x), M(x) is the polynomial corresponding to the original frame and m the bit number.

- x<sup>r</sup>× M(x) must be divided (module 2) by G(x): x<sup>r</sup>× M(x)=G(x)× Q(x)+R(x) the coefficients in R(x) (remainder) will constitute the bit sequence of the checksum.

- Now, the remainder R(x) is added (module 2) to x<sup>r</sup> × M(x) achieving the new bit frame that must be transmitted provided also with the right checksum.

The generator of cyclic codes cannot be a whatever polynomial. Generally speaking it is possible to obtain the same R(x) starting from different M(x) dividend polynomials. All those polynomials that give the same R(x) when divided by the same G(x) generator are defined as *congruous module* G(x). This approach does not detect those errors that transforms the transmitted bit sequence in a different one that however replicate a congruous polynomial. In any case it is a very efficient method for error recognition.

#### •RS 232 C STANDARD INTERFACE (1969)

```

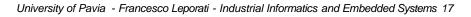

Cannon connector with 25 or 9 poles

```

Allowed length from few meters until tenths

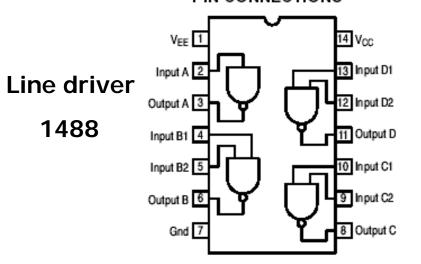

Negative logic voltage levels: "0" (3V ? 25V) / "1" (-3V ? -25V). Usually +12 V e -12 V are used. Wide noise immunity range but not ground reference

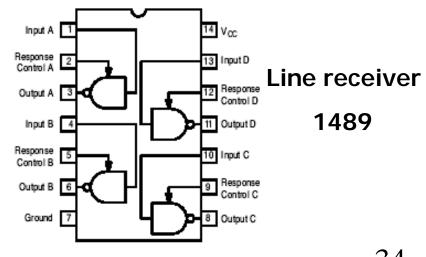

TTL signals must be converted in voltage levels compliant with RS232 values: line drivers and receivers must be employed

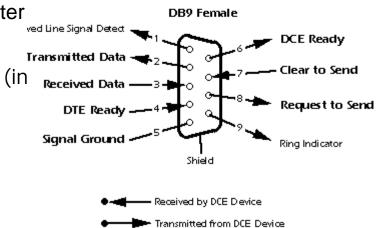

#### PIN CONNECTIONS

PIN CONNECTIONS

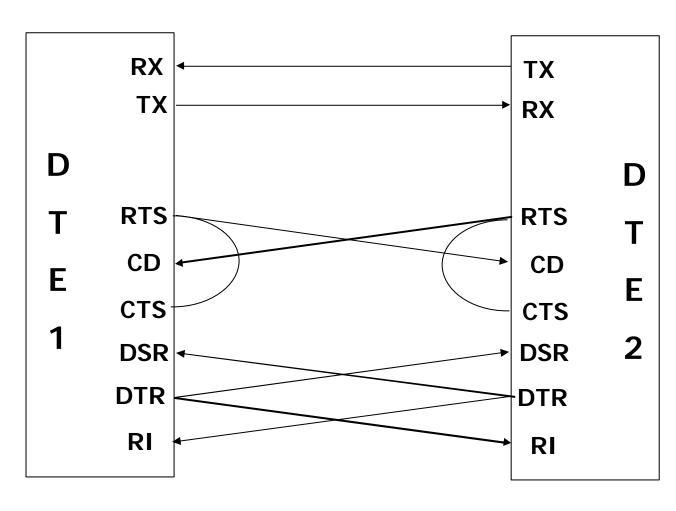

#### •RS 232 C STANDARD INTERFACE (1969)

Proposed for the first time in '60s by Electronic Industry Association (EIA) and then upgraded several times (last in '97) but still used in industrial manufacturing

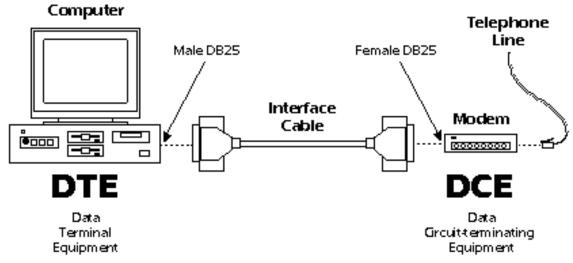

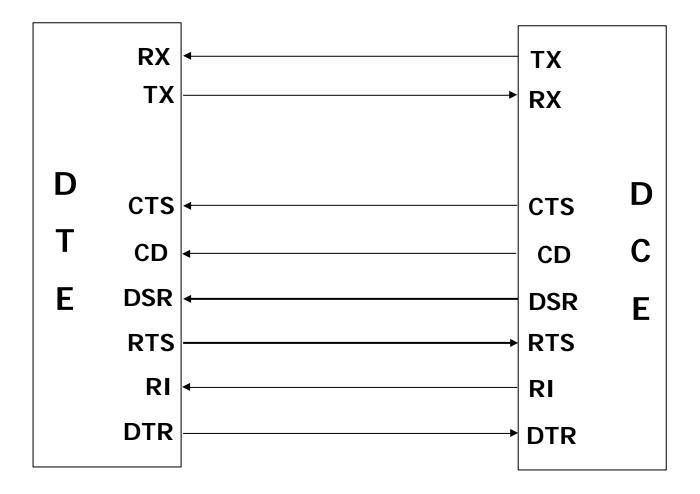

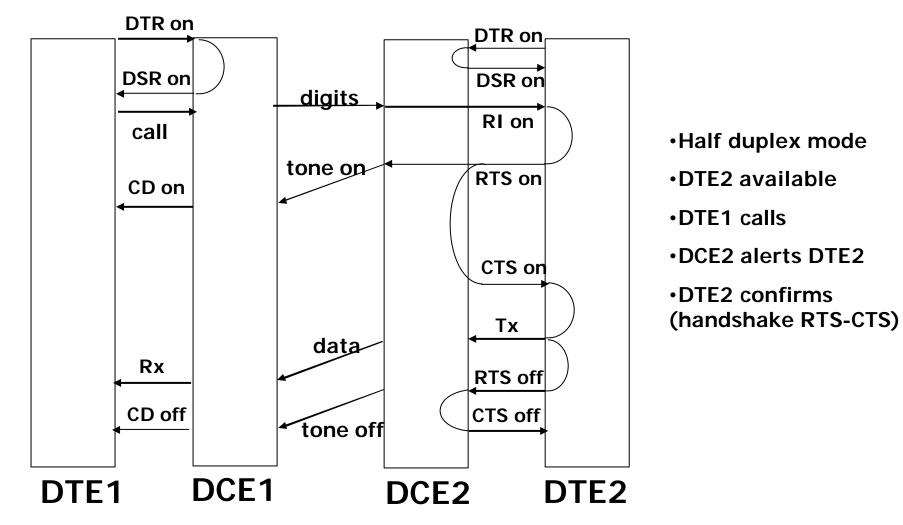

The connection model is among so-called Data Terminal Equipments (DTE) (typically computers connected through modems) and DCE - Data Communication Equipments (peripherals connected through modems)

Half duplex and full duplex communications

Null modem version as direct connection between DTE devices

University of Pavia - Francesco Leporati - Industrial Informatics and Embedded Systems 17

### •RS 232 C PINOUT

- 1-7: Signal ground (AB)

- 2: Transmitted data (TxD): data output

- 3: Received data (RxD): data input

- 4: *Request-to-send (RTS)*: DTE ready to transmit (out in DTE and in DCE)

- 5: *Clear-to-send (CTS)*: DCE ready to receive (out in DCE and in DTE)

- 6: DCE ready (DSR): modem ready to start communication

- 8: Received line signal detector (CD): a remote

transmitting modem is detected

- 15: TXC (Transmit Clock): clock generated by the transmitter

- (in case of isochronous synchronization)

- 17: RXC (Receive Clock): clock generated by the receiver (in

- case of isochronous synchronization)

- 20: DTE ready (DTR): DTE ready to receive

- 22: Ring Indicator (RI): modem alerts DTE about a call

#### DTE-DCE connection

•Setup call

#### Data transfer and end of the call

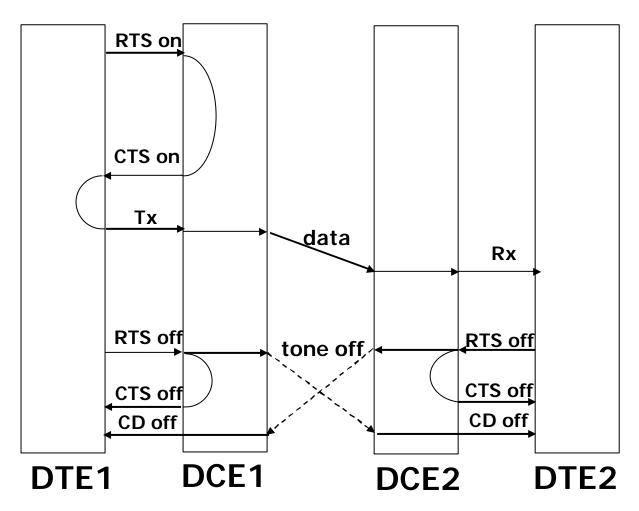

•DTE1 answers (handshake RTS-CTS) ...

•... and sends those data of which the communication consists

•At the end, one of the DTEs closes the connection with a closing handshake so terminating the communication session

#### •Null-modem half duplex connection (if DTE close)

University of Pavia - Francesco Leporati - Industrial Informatics and Embedded Systems 17

•On the contrary, if full duplex is selected only DTR/DSR/CD and not RTS/CTS are used. DTE1 verifies if DSR of DTE2 is active (ready to work). If yes, DTE1 samples the CD pin to verify the eventual presence of a carrier signal on the line (the partner is trying to communicate) otherwise it starts to communicate.

• If the isochronous temporization is selected pins 15 (TXC) and 17 (RXC) must be used. The transmission clock is used to generate data in isochronous mode, travels with them and will be brought on the RXC pin of the recipient.

#### RS232 final considerations

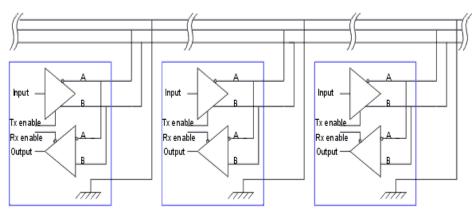

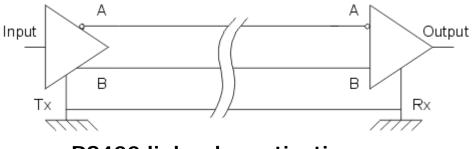

- Popular variants of the RS232 are RS422 and RS485.

- In the first case velocities up to 10 Mbit/sec are achieved on distances close to the Km.

- The transmission is in "differential" mode that is using voltage levels slightly different from 232 (A<B "1" e A>B "0") therefore level converters must be introduced.

- •Up to 10 recipients connected to a single transmission driver are allowed.

**RS485** link schematization

University of Pavia - Francesco Leporati - Industrial Informatics and Embedded Systems 17

**RS422 link schematization**

• The RS 485 is very similar to the 422 from the electric point of view, but allows the coexistence of several couples Tx/Rx on the same transmission line (multi-point), although only one transmitter at a time can be active.

- Up to 32 recipients are allowed.

- Velocities within 100 Kb/sec and 10 Mb/s.

- Distances within 1200 m and 15 m.

- •Used when connecting PC, PLC and instrumentations in a bus topology.

#### Characteristics of RS485 compared to RS232, RS422 and RS423

|                                       | RS232          | RS423       | RS422       | RS485       |

|---------------------------------------|----------------|-------------|-------------|-------------|

| Differential                          | no             | no          | yes         | yes         |

| Max number of drivers                 | 1              | 1           | 1           | 32          |

| Max number of receivers               | 1              | 10          | 10          | 32          |

| Modes of operation                    | half duplex    |             |             |             |

|                                       | full duplex    | half duplex | half duplex | half duplex |

| Network topology                      | point-to-point | multidron   | multidrop   | multipoint  |

|                                       | 15 m           | 1200 m      | 1200 m      | 1200 m      |

| Max distance (acc. standard)          | -              |             |             |             |

| Max speed at 12 m                     | 20 kbs         | 100 kbs     | 10 Mbs      | 35 Mbs      |

| Max speed at 1200 m                   | 1 kbs          | 1 kbs       | 100 kbs     | 100 kbs     |

|                                       |                |             |             |             |

| Max slew rate                         | 30 V/µs        | adjustable  | n/a         | n/a         |

| Receiver input resistance             | 37 k?          | 4 k?        | 4 k?        | 12 k?       |

| Driver load impedance                 | 37 k?          | 450 ?       | 100 ?       | 54 ?        |

| Receiver input sensitivity            | ±3 V           | ±200 mV     | ±200 mV     | ±200 mV     |

| Receiver input range                  | ±15 V          | ±12 V       | ±10 V       | –712 V      |

| Max driver output voltage             | ±25 V          | ±6 V        | ±6 V        | –712 V      |

| Min driver output voltage (with load) | $\pm 5 V$      | ±3.6 V      | ±2.0 V      | $\pm 1.5$ V |

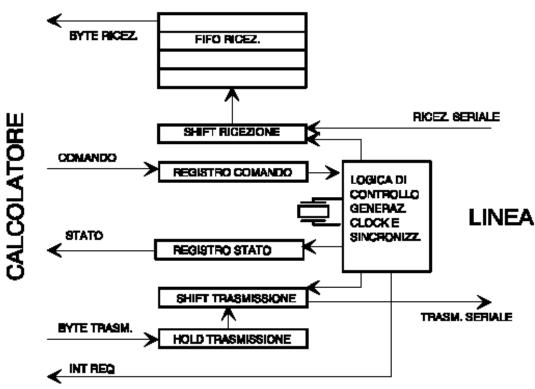

USART (Universal Synchronous Asynchronous Receiver Transmitter)

IC carrying out synchronous/asynchronous serial transmission

•Sometimes embedded within the microcontroller? single chip computer

•UART if the transmission is only asynchronous

•The device implements all the transmission/reception task, temporization, parity check ..., while the voltage level adaptation is done through suitable driver

•Basic structure made up by:

- transmission and reception buffers

- transmission and reception shift register

- mode, command, state registers

•COTS standard devices: NS8250 e NS16550

#### **USART** : block scheme

A character put in the *transmission register* triggers the beginning of the transmission

The reception is performed by reading the *receiving register* where data are valid if suitable error flags are not active in the *status register*

The state register bits indicate:

- FA if synchronization has been done

- if the transmission buffer is empty

- if transmission shift reg. is empty

- if a character is in reception buffer

- errors (parity, framing, overrun)

- interrupt

Command reg.: reset state indicators, enable interrupt, set line signals (RTS ...

Mode reg.: set of the comm. velocity, parity, synchronization characters

#### UART 8250: registers

8 registers in 8 consecutive address areas of the I/O memory space (base address = 3F8H for Com1 and 2E8H for Com2 ports)

some registers can be used in sole reading mode or in sole writing mode if the bit DLAB in LCR is zero or in both the R/W modes if the bit DLAB=1

| Indirizzo | Read                | Write                   | Read               | Write  |

|-----------|---------------------|-------------------------|--------------------|--------|

| base      | RBR (rec. buf.)     | THR (transm. hold)      | DLL (divisor latch | LSB)   |

| base+1    | IER (int. enab.)    | IER                     | DLM (divisor latch | ר MSB) |

| base+2    | IIR (int. identif.) | FCR (fifo control)      | IIR                | FCR    |

| base+3    | LCR (line c         | ontrol, R/W independen  | tly on DLAB)       |        |

| base +4   | MCM (mod            | em control, R/W indepe  | endently on DLAB)  |        |

| base+5    | LSR (line status)   | /                       | LSR                | /      |

| base+6    | MSR (modem status)  | /                       | MSR                | /      |

| base+7    | SCR (scrate         | ch, R/W independently o | on DLAB)           |        |

| UART 8250: registers                                    | Baud Rate<br>110<br>300 | High Byte<br>04H<br>01H | Low Byte<br>17H<br>80H |

|---------------------------------------------------------|-------------------------|-------------------------|------------------------|

|                                                         | 1200                    | 00H                     | 60H                    |

| DLR = Divisor Latch Register                            | 2400                    | 00H                     | 30H                    |

| DER - Divisor Eutori Rogistor                           | 4800                    | 00H                     | 18H                    |

| 16 bit registers used to set the baud rate on the basis | 9600                    | 00H                     | 0CH                    |

| of the values written in BA e BA+1                      | 19200                   | 00H                     | 06H                    |

|                                                         | 38400                   | 00H                     | 03H                    |

|                                                         | 57600                   | 00H                     | 02H                    |

|                                                         | 115200                  | 00H                     | 01H                    |

b2

b1

0

0

b7...b4 - Reserved always zero b3 - Modem Status Interrupt

- b3 Modern Status Interrupt

- b2 Receiver Line Status Interrupt

- b1 Transmitter Holding Register Empty Interrupt

- b0 Received Data Available Interrupt

#### IER = Interrupt Enable Register

enable UART to generate interrupt through setting of the correspondent bits

### IIR = Interrupt Identification

| Register                        | 1 |

|---------------------------------|---|

| the bit allows to identify the  | 1 |

| origin of the interrupt service | 0 |

| request                         | 0 |

| What they say                | How to reset          |

|------------------------------|-----------------------|

| Receiver Line Status         | Read LSR              |

| Received Data Available      | Read RBR              |

| Transm. Hold. Register Empty | Read IIR or write THR |

| Modem Status                 | Read MSR              |

|                              | _                     |

b0= int. pending; b3= int. time out

46

#### FCR = Fifo Control Register

8 bit register used to setup the Fifo memories present in the 16550 device: in particular b0 enables the Fifo, b1 and b2 empty reception and transmission Fifos, b6 and b7 define the n° of bytes required to set the full Fifo flag (1, 4, 8, 14)

#### LCR = Line Control Register

8 bit register to set different functionalities

b7 (DLAB) = if 1 allows to access DLR, if 0 to access RBR, THR, IER

b6 = if 1, a constant voltage level corresponding to that of a start bit is put on the line to signal a break of transmission.

b4, b3 = set the parity

- b2 = set the number of stop bits (1, 2)

- b1, b0 = set the character length (5, 6, 7, 8 bit)

MCR = Modem Control Register

8 bit register used to set the RTS and DTR signal output from the UART:

- **b2** = global enable of the UART to interrupt

- b1, b0 = if 1 each one activates RTS and DTR

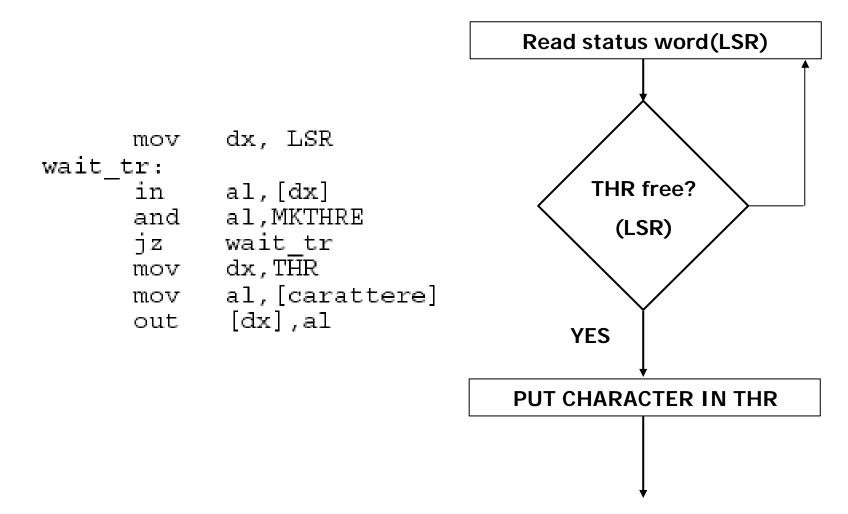

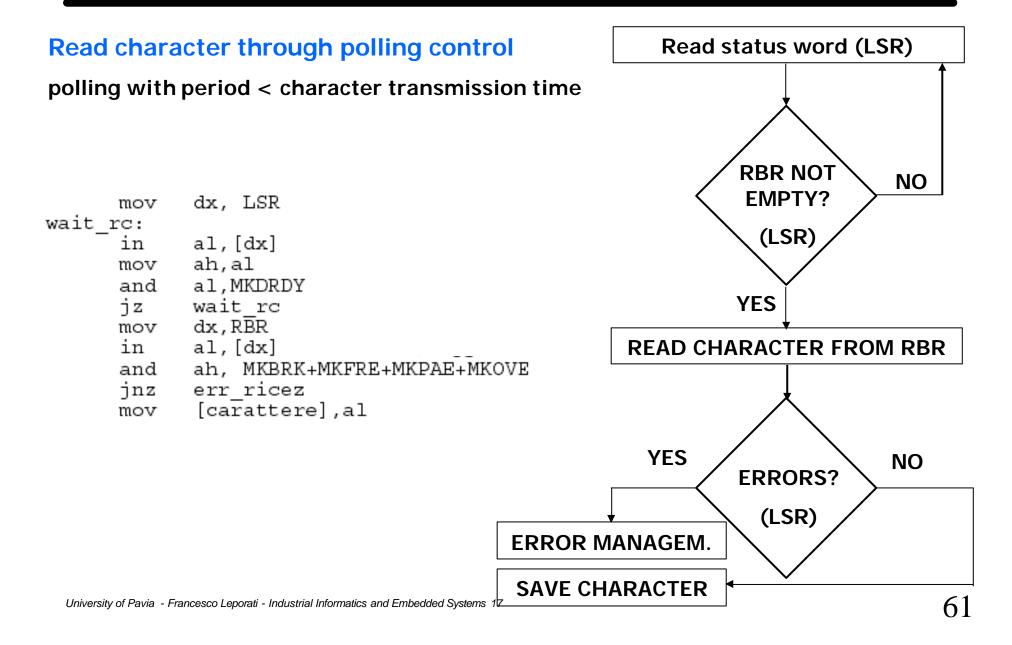

#### LSR = Line Status Register

8 bit register providing info about the transmission status

b5 = 1 if the THR register is empty. The corresponding interrupt is activated, if enabled

b4 = 1 if a low level is detected on the line (Break) longer than a character

b3 = 1 if after the character bits and the parity the expected stop bit is not detected (Framing Error)

b2 = 1 if after the character bits the parity is not correct (Parity Error)

- b1 = 1 if a character in RBR has been overwritten before being read (Overrun Error)

- b0 = 1 if a new, not read character is available in RBR (becomes 0 after reading)

#### MSR = Modem Status Register

8 bit register used to detect the value of the CD, RI, DSR e CTS (b7-b4) signals or if they were switched (b3-b0)

#### SCR = Scratch Register

Service register to read/write temporary values

#### **USART sw management**

#### Polling

- •The LSR is periodically polled: a new received character or a character to be transmitted or error will be signaled

- Low-medium communication velocities and busy waiting

#### Interrupt

- •Each of the three previous situations generates an interupt request (character reception, character transmission, error)

- •IIR is read to adequately serve the interrupt

- Medium transmission velocities (9600 baud)

#### DMA

- controllers or coprocessors devoted to handshake between memory and USART

- velocities in the order of MB/sec

- Not always provided: only in expensive devices

#### **USART sw management**

# Init registers addresses and main masks for bits

| BA E                                                                            | EQU                                    | 3F8H                                           |                                        | ;indirizzo base                                                                                                                                                              |

|---------------------------------------------------------------------------------|----------------------------------------|------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                 | ZQU<br>ZQU                             | BA+0<br>BA+0                                   |                                        | ;dato ricevuto<br>;dato da trasmettere                                                                                                                                       |

| DLRL E<br>DLRH E<br>B1200 E<br>B9600 E                                          | EQU<br>EQU                             | BA+0<br>BA+0<br>0060H<br>000CH                 |                                        | ;seleziona baud L<br>;seleziona baud H<br>;valore per 1200 baud<br>;valore per 9600 baud                                                                                     |

| IER E<br>MKEIT E<br>MKEIR E                                                     |                                        | BA+1<br>2<br>1                                 |                                        | ;reg. abilitaz. interrupt<br>;maschera int. trasmissione<br>;maschera int. ricezione                                                                                         |

|                                                                                 | EQU<br>EQU                             | BA+2<br>6                                      |                                        | ;reg. tipo interrupt<br>;maschera bit di tipo                                                                                                                                |

| FCR E<br>MKF1 E<br>MKF4 E<br>MKF8 E<br>MKF14 E<br>MKFRT E<br>MKFRR E<br>MKFRN E | SQU<br>SQU<br>SQU<br>SQU<br>SQU<br>SQU |                                                |                                        | ;reg. controllo FIFO<br>;int. ogni byte<br>;int. ogni 4 byte<br>; 8 byte<br>; 14 byte<br>;mschera reset FIFO trasm.<br>;maschera reset FIFO ricez.<br>;maschera abilita FIFO |

| LCR E<br>MKDLAB<br>STDLINE                                                      | EQU<br>E                               | BA+3<br>EQU<br>EQU                             | 80H<br>1BH                             | ;reg. controllo linea<br>;impostaz. standard pari, 1 stop, 8 bit                                                                                                             |

| MCR E                                                                           | ZQU                                    | BA+4                                           |                                        |                                                                                                                                                                              |

| LSR E<br>MKTHRE<br>MKBRK<br>MKFRE<br>MKPAE<br>MKOVE<br>MKOVE<br>MKDRDY          | ΩU                                     | BA+5<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU<br>EQU | 20H<br>10H<br>08H<br>04H<br>02H<br>01H | ;reg. stato linea<br>;maschera THRE<br>;maschera Break<br>;maschera framing err.<br>;maschera parity err.<br>;maschera overrun err.<br>;maschera dato ricevuto ready         |

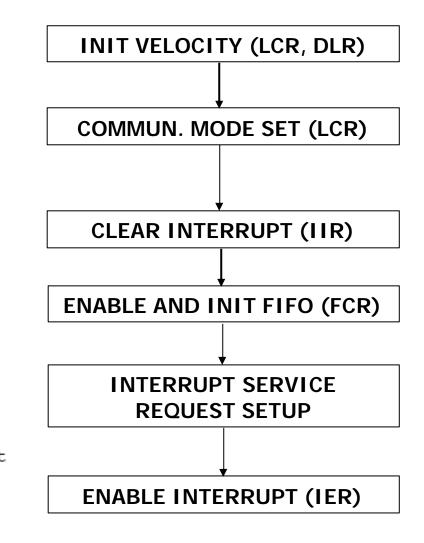

#### **UART** setup

;imposta velocita' di comunicazione AL, MKDLAB MOV MOV DX, LCR OUT [DX],AL MOV AX, B9600 MOV DX, DLRL OUT [DX],AL INC DX [DX],AH OUT :imposta modalita' di comunicazione AL, STDLINE MOV DX,LCR MOV OUT [DX],AL ;cancella eventuali interrupt pendenti DX, IIR MOV AL, [DX] IN;inizializza la FIFO e la abilita AL, MKFRT+MKFRR+MKFEN MOV DX, FCR MOV [DX],AL OUT ;aggancia la routine di servizio interrupt CALL AGGANCIA INT UART ;abilita UART a generare richieste di interrupt MOV AL, MKEIT+MKEIR DX, IER MOV [DX],AL OUT

Aggancia\_INT\_UART

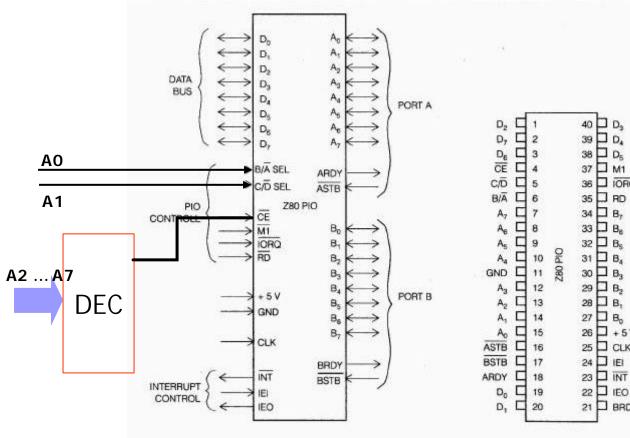

• The parallel port of a typical microprocessor

|                               | B/A: select port B o A                   |

|-------------------------------|------------------------------------------|

|                               | CE: chip enable                          |

|                               | M1: fetch active                         |

|                               | IEO/IEI: interrupt en.                   |

| )3<br>)4<br>)5<br>(11<br>)0RQ | A/B RDY: port ready to<br>communicate    |

| ND<br>Iy<br>Na                | A/B STB: peripheral ready to communicate |

| 34<br>33<br>32                | INT: int. request                        |

| l,<br>l₀<br>-5V               | IORQ: mem. mapped I/O                    |

| ELK<br>El                     | C/D: command or data                     |

| eo<br>Irdy                    | RD: read o write                         |

|                               | A0-A7: out port A                        |

|                               | BO-B7: out port B                        |

|                               | 53                                       |

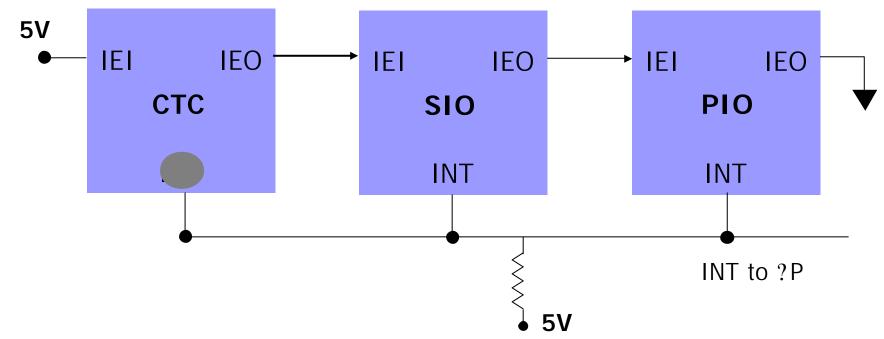

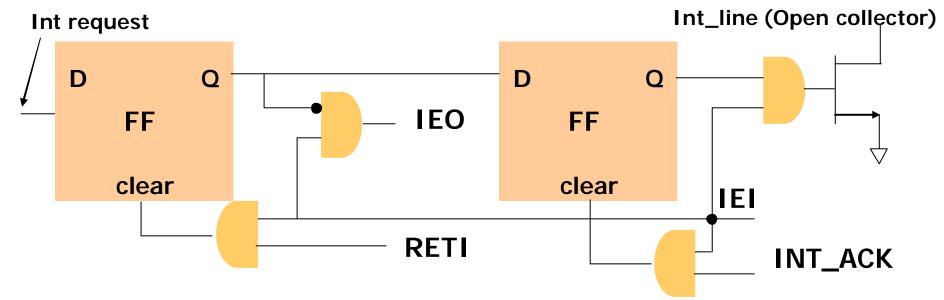

• A hardware priority chain: *daisy chain* (priority diminishes from left to right)

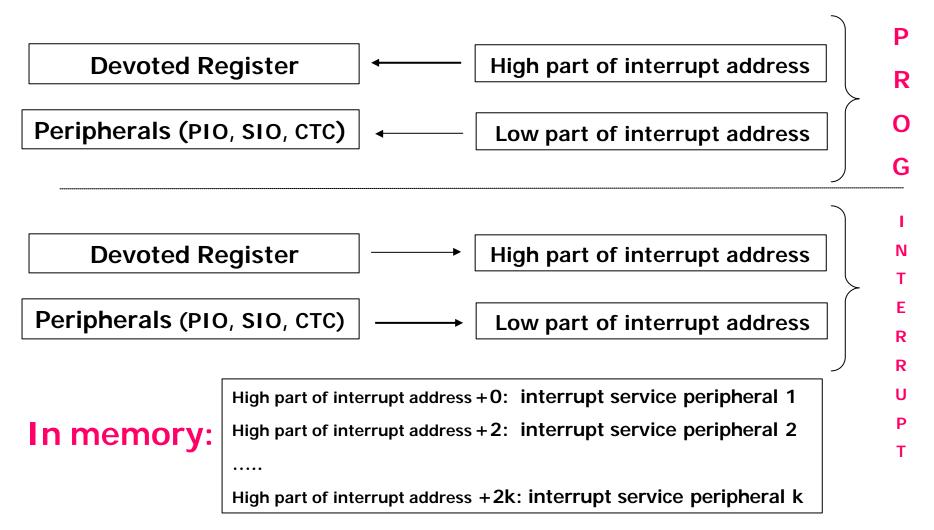

When a peripheral (parallel, serial, timer) generates an interrupt the ?P can recognize the request and sets M1 and IORQ lines simultaneously at zero (IntAck).

The peripherals, looking two lines at zero, will put on the bus the low part of the interrupt vector (specific for itself). The PIO must be connected with the M1 e IORQ lines to know that the microprocessor acknowledged the interrupt.

Interrupt request management on each peripheral connected in daisy chain

- The first FF receives a service request that is passed to the II FF only if the IEI signal is active. In this case the II FF forces the MOS commutation by activating the interrupt line (supposed low) that is managed in a open collector fashion.

- Int\_ack clears only the port enabled to request (who has been already serviced does not must require anymore, who is waiting keeps its request still active).

- The RETI instruction (executed when the interrupt routine ends) clears the first FF (the one that maintains its request active).

•PIO port programming (modes 0, 1, 2)

A port can be configured to work in mode 0 (output only), 1 (input only), 2 (bidirectional) or 3 (bit by bit). This is possible by writing suitable bytes to the port that however must be set in "command" (configuration) mode (C/D=1).

The first three modes require a control word into which the configuration bits setting mode 0, 1 or 2 are coded in bits D7 and D6

M2 | M1 | X | X | 1 | 1 | 1 | 1

Then the low part of the interrupt vector (address) will be sent to the port (that is the value given back by the port itself on the data bus when it will require an interrupt service).

Finally it will be possible to disable the interrupt for that port by sending the following word with the bit 7 set to 1 (enable) or to 0 (disable).

•PIO port programming (mode 3)

In mode 3 the same procedure is followed as before that sends a *mode control* word and the interrupt vector to the port.

Then a word is sent that specifies what bits are in input (set to 1) and what in output (set to 0); for instance below the bits 7-6-3-2-1-0 are set as input and 5-4 as output.

1 | 1 | 0 | 0 | 1 | 1 | 1 | 1

The *interrupt control word* features the following format into which the bit D4 specificies if inputs must be masked or not i. e. if all of them (0) or only few (1) will cause interrupt service request. In this case a mask will follow that indicate what bit will generate the interrupt (0) and what ones must be ignored.

The bit D5 indicated the interrupt activation edge (0 falling / 1 raising), D6 if the generating condition is the OR or the AND of more bits, and D7 if the interrupt request is enabled or not.

|               | NAME MAIN                                                                                                | 8 000A LENGA EQU 0AH ;length tab. prog. SIOA                         |   |

|---------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|---|

| 4 0000        |                                                                                                          | 8 000C LENGB EQU 0CH ; lenght tab. prog. SIOB                        |   |

| 6             | LIST E,O,S,T                                                                                             | 8 0020 SIOA EQU 20H                                                  |   |

| 7 0000        |                                                                                                          | 8 0021 SIOB EQU 21H                                                  |   |

| 8             | INCLUDE COST.H ; equates                                                                                 | 8 0022 SIOAC EQU 22H                                                 |   |

| 8 0030        | TABINT EQU 30H ;most sign. byte in the address of interrupt tab.                                         | 8 0023 SIOBC EQU 23H                                                 |   |

| 8 0040        | PIO1A EQU 40H                                                                                            | 8 00F0 SIOVEC EQU 0F0H ;tab. interrupt SIO                           |   |

| 8 0042        | PIO1AC EQU 42H                                                                                           | 8 00FF LCD_C EQU 0FFH ;address command/state LCD                     |   |

| 8 0041        | PIO1B EQU 41H                                                                                            | 8 00FE LCD_D EQU 0FEH ;address dat LCD                               |   |

| 8 0043        | PIO1BC EQU 43H                                                                                           | 30 0000                                                              |   |

| 8 0060        | PIO2A EQU 60H                                                                                            | 31 CSEG                                                              |   |

| 8 0062        | PIO2AC EQU 62H                                                                                           | 33 0000 F3 DI                                                        |   |

| 8 0061        | PIO2B EQU 61H                                                                                            | 34 0001                                                              |   |

| 8 0063        | PIO2BC EQU 63H                                                                                           | 35 0001 CD BE 06 C CALL RITARDO                                      |   |

| 8 0000        |                                                                                                          | 36 0004 31 FF F7 LD SP,STAC                                          |   |

| 8 000F        | MODOO EQU OFH                                                                                            | 47 0022 ED B0 LDIR                                                   |   |

| 8 004F        | MODO1 EQU 4FH                                                                                            | 48 0024 08 EX AF,AF'                                                 |   |

| 8 008F        | MODO2 EQU 8FH                                                                                            | 49 0025 D9 EXX                                                       |   |

| 8 00CF        | MODO3 EQU OCFH                                                                                           | 50 0026                                                              |   |

| 8 0007        | DISINT EQU 07H ; disable interrupt                                                                       | 51 0026 CD CB 03 C CALL RETI ;reset hw all peripherals (4)           |   |

| 8 0083        | LIN2A EQU 83H ; ISOL REEDB input, ADC-BSY input                                                          | 52 0029 CD CB 03 C CALL RETI                                         |   |

| 8 00A7        | CNINTP EQU 0A7H ; int. abil., OR, high edge active                                                       | 53 002C CD CB 03 C CALL RETI                                         |   |

| 8 00FE        | MASK EQU OFEH ; the line D0 only activates interrupt                                                     | 54 002F CD CB 03 C CALL RETI                                         |   |

| 8 0000        | CTCCH0 EQU 00H ;channel 0 CTC                                                                            | 55 0032 ED 5E IM 2 ;vector interrupt mode set                        |   |

| 8 0001        | CTCCH1 EQU 01H ;channel 1 CTC                                                                            | 56         0034         3E         30         LD A, TABINT           |   |

| 8 0002        | CTCCH2 EQU 02H ;channel 2 CTC                                                                            | 57 0036 ED 47 LD I,A                                                 |   |

| 8 0003        | CTCCH3 EQU 03H ;channel 3 CTC                                                                            | 58 0038                                                              |   |

| 8 0007        | CTCCN2 EQU 07H ;no int, timer mode, prescaler=16, whatever edge                                          | 59 ; Programming PIO, CTC, SIO                                       |   |

| 8             | ;no trigger, time constant follows, reset                                                                | 60 ; inizialization PIO                                              |   |

| 8 00C7        | CTCCN3 EQU 0C7H ;enable int., counter mode, no prescaler, neg. edge                                      | 61 ; ***********************************                             |   |

| 8             | ;no trigger, time constant follows, reset                                                                | 62 0038 3E 07 LD A,DISINT                                            |   |

| 8 0017        | SIOCNT EQU 17H ; control for SIO temporization                                                           | 63 003A D3 42 OUT (PIO1AC),A                                         |   |

| 8             | ;through CTC outputs, no int,. timer mode                                                                | 64 003C D3 43 OUT (PIO1BC),A                                         | _ |

| 8             | ;16, positive edge, time constant follows, reset                                                         | 65 003E D3 63 OUT (PIO2BC),A ;disab. interrupt on PIO1A, PIO2B, PIO1 | 3 |

| University of | Pavia <sup>TIME</sup> ranEesco Legorát <sup>I C</sup> Industrial Infermatiles (and Efribedded Systems 17 | 66 0040<br>67 0040 3E 0F LD A,MODO0 58                               | 2 |

| 8 0028        | TIME3 EQU 40 ;CTC time constant channel 3                                                                | •••                                                                  | , |

| 8 0001        | BAUD EQU 1 ;temp. channels 0 and 1 CTC (9600 baud)                                                       | 68 0042 D3 63 OUT (PIO2BC),A                                         |   |

|               |                                                                                                          |                                                                      |   |

| 69 0044 D3 43      | OUT (PIO1BC),A                                                | 520 0398 EE 20                | XOR 20H ; test bit D5 edge sensitiv      | ə          |

|--------------------|---------------------------------------------------------------|-------------------------------|------------------------------------------|------------|

| 70 0046 3E 30      | LD A,30H ;READ e WRITE high to do not write spurious data     | 521 039A D3 62                | OUT (PIO2AC),A                           |            |

| 71 0048 D3 41      | OUT (PIO1B),A                                                 | 522 039C 32 B1 02 D           | LD (PROG2A), A ; to successively program | the port 2 |

| 72 004A            |                                                               | 523 039F                      |                                          |            |

| 73 004A 3E CF      | LD A,MODO3                                                    | 524 039F ED 4B 11 02 D        | LD BC,(CIMP) ;load pulse counter REEL    | В          |

| 74 004C D3 42      | OUT (PIO1AC),A                                                | 525 03A3 3A CE 02 D           | LD A,(KEY)                               |            |

| 75 004E 3E FF      | LD A,0FFH                                                     | 526 03A6 CB 7F                | BIT PWRCLOSB,A                           |            |

| 76 0050 D3 42      | OUT (PIO1AC),A                                                | 527 03A8 C2 AF 03 C           | JP NZ,TRY6                               |            |

| 77 0052            |                                                               | 528 03AB 0B                   | DEC BC                                   |            |

| 78 0052 3E E6      | LD A,0E6H ; LSB interrupt routine                             | 529 03AC C3 B5 03 C           | JP CARICA                                |            |

| 79 0054 D3 62      | OUT (PIO2AC),A                                                | 530 03AF CB 77 TRY6           | BIT PWROPENB,A                           |            |

| 80 0056 3E CF      | LD A,MODO3 ; PIO 3 mode                                       | 531 03B1 C2 B5 03 C           | JP NZ,CARICA                             |            |

| 81 0058 D3 62      | OUT (PIO2AC),A                                                | 532 03B4 03                   | INC BC                                   |            |

| 82 005A 3E 83      | LD A,LIN2A ; what input/output lines                          | 533 03B5 ED 43 11 02 D CARICA | LD (CIMP), BC                            |            |

| 83 005C D3 62      | OUT (PIO2AC),A                                                | 534 03B9 D9                   | EXX                                      |            |

| 84 005E 3E A7      | LD A,CNINTP ; interrupt control                               | 535 03BA 08                   | EX AF,AF'                                |            |

| 85 0060 32 B1 02 D | LD (PROG2A),A ; port 2A re-programmed in interrupt            | 536 03BB FB                   | EI                                       |            |

| 86 0063 C6 10      | ADD A,10H ; a mask will follow                                | 537 03BC ED 4D                | RETI                                     |            |

| 87 0065 D3 62      | OUT (PIO2AC),A                                                | 538 03BE                      |                                          |            |

| 88 0067 3E FE      | LD A,MASK ; mask for those lines activating interrupt         |                               |                                          |            |

| 89 0069 D3 62      | OUT (PIO2AC),A                                                | 1078                          | ORG 30E6H                                |            |

| 90 006B            |                                                               | 1079 30E6                     |                                          |            |

| 91 ; init CTC      |                                                               | 1080 30E6 93 03 C             | DEFW PIOINT                              |            |

| ; init SIO         |                                                               | 1081 30E8 12 05 C             | DEFW EIRETI                              |            |

| ; ******           | *****                                                         | 1082 30EA 12 05 C             | DEFW EIRETI                              |            |

| 147                |                                                               | 1083 30EC 12 05 C             | DEFW EIRETI                              |            |

| 48 00C6            |                                                               | 1084 30EE 69 01 C             | DEFW CTCINT                              |            |

| 49 00C6 FB MAIN:   | EI                                                            | 1085 30F0 CD 03 C             | DEFW TRASB                               |            |

| 257 0168 C9        | RET                                                           | 1086 30F2 D9 03 C             | DEFW EXTB                                |            |

| 513 0393           |                                                               | 1087 30F4 E3 04 C             | DEFW RICEB                               |            |

| 514                |                                                               | 1088 30F6 0A 05 C             | DEFW SPECB                               |            |

| 15                 |                                                               | 1089 30F8 BE 03 C             | DEFW TRASA                               |            |

| 516                |                                                               | 1090 30FA E4 03 C             | DEFW EXTA                                |            |

| ******             | ***************************************                       | 1091 30FC EF 03 C             | DEFW RICEA                               |            |

| 517 0393 08 PIOIN  | T EX AF,AF'                                                   | 1092 30FE EA 04 C             | DEFW SPECA                               |            |

| 18 0394 D9         | esco Leporati - Industrial Informatics and Embedded Systems 1 | -                             |                                          | 5          |

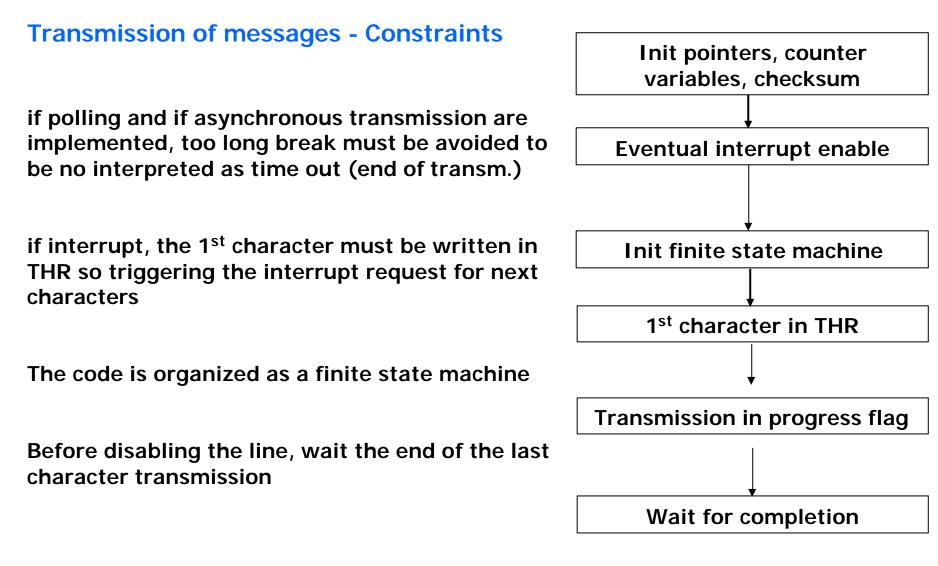

#### Transmission of a character through polling control

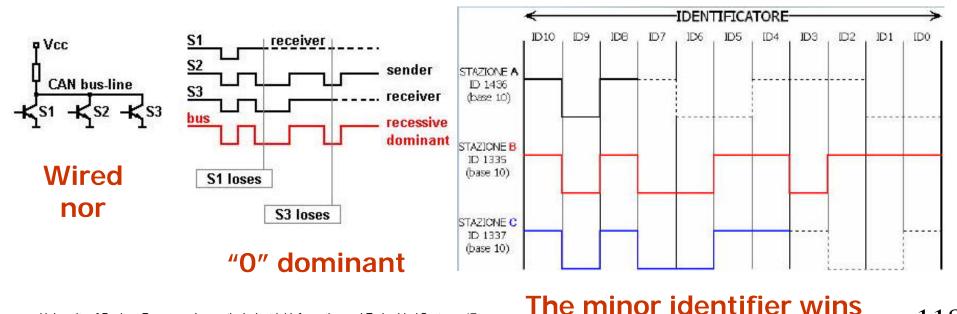

#### Message format

```

Structured as "container" + "content"

```

```

Container = "header"+ "trailer"

```

Initial characters = Start of message (1/2 bit)

Destination code for multipoint connections. Multicast and broadcast possible

Total n° of characters to establish the end of a binary message

Sender code (in particular for multipoint connections)

Progressive of transmission = order n° of the message (to verify the sequence correctness)

Progressive of reception = order n° of the last correct message received

Function code = the role played in the message by the current received fragment

Data (ASCII/binary)

Verification code = checksum, longitudinal parity or CRC

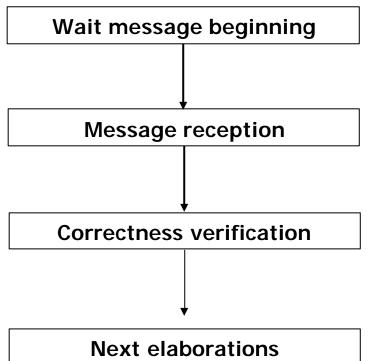

#### Message reception

"Relaxed" wait of the first character and fast reception of the next ones

Reception through polling/interrupt (often the 1° character with polling, the others with polling or interrupt), verification of the correctness and calculation of the verification code

Wait message

Wait message

Correctness

Comparison of the two verification codes

Message elaboration and answer

#### An example: half duplex point-2-point protocol

| Message format in application processes          | tipo<br>ncar<br>test                                     | numero byte di testo $(0 < ncar < 256)$                                                                                                                                                                                                                                         |

|--------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Available functions in application processes     | void put_tra (                                           | void) inizializza la comunicazione<br>mess) inserisce messaggio in coda di trasmissione<br>void) estrae messaggio da coda di ricezione. Se il sistema<br>remoto non aveva nulla da trasmettere si riceve un<br>messaggio di tipo = 0 e contenente un solo byte = 0 di<br>testo. |

| Message format for<br>communication<br>processes | prog_t co<br>prog_r co<br>tipo co<br>ncar nu<br>testo co | rattere iniziale <i>Start Of Header</i><br>dice progressivo del messaggio corrente<br>dice progressivo dell'ultimo messaggio ricevuto correttamente<br>dice tipo messaggio<br>mero byte del testo<br>ntenuto del messaggio<br>ecksum di tutti i byte da SOH escluso             |

#### An example: half duplex point-2-point protocol

| <b>Data structures</b><br>(communication level, 8 | coda_ric coda di messaggi correttamente ricevuti in attesa di essere<br>consumati dai processi applicativi.                                                                                                                                                     |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| characters + parity)                              | coda_tra coda di messaggi prodotti dai processi applicativi e da trasmettere.                                                                                                                                                                                   |

|                                                   | buf_ric array di caratteri per la ricezione del messaggio corrente.                                                                                                                                                                                             |

|                                                   | buf_tra array di caratteri per la trasmissione del messaggio corrente.                                                                                                                                                                                          |

| Communication                                     | mess get_tra (void) estrae messaggio dalla coda di trasmissione. Se la coda è vuota si invia un messaggio di tipo vuoto (=0) con un solo byte (=0).                                                                                                             |

| procedures                                        | void put_ric (mess) inserisce messaggio nella coda di ricezione                                                                                                                                                                                                 |

|                                                   | <pre>interrupt int_ric () funzione chiamata da interrupt di ricezione, cioè<br/>quando si è ricevuto un carattere o si ha un errore in ricezione. Organizzata<br/>come automa a stati che evolve con l'andamento del messaggio in corso di<br/>ricezione.</pre> |

|                                                   | <pre>interrupt int_tra () funzione chiamata da interrupt di trasmissione,<br/>cioè quando si ha Transmit Register Empty. Organizzata come automa a stati<br/>che evolve con l'andamento del messaggio in corso di ricezione.</pre>                              |

|                                                   | int leggi_tempo (void) lettura tempo corrente, usata per il rilievo di<br>time-out di fine messaggio                                                                                                                                                            |

#### An example: half duplex point-2-point protocol

| Communication<br>level variables | char        | _                        | lell'automa di trasmissione<br>lell'automa di ricezione<br>codice progressivo di trasmissione del sistema remoto<br>codice progressivo di trasmissione del sistema locale<br>codice progressivo di ricezione del sistema remoto<br>codice progressivo di ricezione del sistema locale<br>checksum corrente del messaggio in trasmissione<br>checksum corrente del messaggio in ricezione<br>numero caratteri del testo da ricevere |

|----------------------------------|-------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | int<br>long | it<br>ir<br>int          | indice corrente del buffer di trasmissione<br>indice corrente del buffer di ricezione                                                                                                                                                                                                                                                                                                                                              |

|                                  |             | tempo_prec<br>tempo_corr | tempo di ricez. carattere precedente (per t-out)<br>tempo di ricez. carattere attuale (per t-out)                                                                                                                                                                                                                                                                                                                                  |

In the following slides an example of code managing message reception and transmission interrupt after interrupt vectorization routines having been settled together with initialization of registers and identification through IIR of the interrupt origin

#### An example: half duplex point-2-point protocol – Reception interrupt

```

void leggi byte uart (void)

byte = leggi rbr (); // registro ricezione UART

errori = check lsr (); // line status per verif

if (errori)

{tempo prec = leggi tempo (); // tempo arrivo by

stato r = S ER;

switch (stato r)

{case S0:

if (bvte == SOH)

stato r = S1;

else

{tempo prec = leggi tempo (); // t arrivo

stato r = S ER;}

break;

case S1: // aspetta progressivo trasmesso remoto

cks r = 0; // azzera checksum

// indice buffer a inizio

ir = 0:

proq t r = byte;

cks r += byte;

stato r = S2;

break;

case S2: // aspetta progressivo ricevuto remoto

proq r r = byte;

cks r += byte;

stato r = S3;

break:

case S3: // aspetta codice tipo

buf ric [ir] = byte;

ir++;

cks r += byte;

stato r = S4;

```

University of Pavia - Francesco Leporati - Industrial Informatics and Embedded Systems

break;

```

case S4: // aspetta numero byte testo (>=1)

buf ric [ir] = byte;

ir++;

count = byte;

cks r += byte;

stato r = S5;

break;

case S5: // aspetta i byte del testo

buf ric [ir] = bvte;

ir++;

cks r += byte;

if \overline{(--count} == 0)

stato r = S6;

break:

case S6: // aspetta byte di checksum

if (byte == cks r)

// verifica checksum

{put ric (buf ric);

// nuovo messaggio corretto

prog r l = prog_t_r;

disab ric ();

// abilita trasmissione

enab tra ();

stato r = S0;

else

// errore checksum

{tempo prec = leggi tempo (); // t arrivo byte

stato r = S ER;

break;

/* ERRORE - Lascia passare, ignorandoli, tutti gli eventuali

caratteri rimanenti e aspetta l'inizio del messaggio successivo

riconosciuto dal carattere SOH ricevuto dopo lo scadere di time-o

*/

case S ER:

// ERRORE -

tempo corr = leggi tempo (); // tempo arrivo byte

if (((tempo corr-tempo prec)>=TOUT) && (byte==SOH))

stato r = S1;

else

tempo prec = tempo corr;

break;

```

#### An example: half duplex point-2-point protocol – Transmission interrupt

```

void scrivi byte uart (void)

switch (stato t)

case S0:

{/* vede se l'ultimo messaggio trasmesso e' stato

ricevuto correttamente da sistema remoto */

if (prog r r == prog t l)

prog t l++;

buf tra = get tra (); // nuovo messaggio

if (buf tra == NULL)

// nulla da trasmet

{buf tra[0] = 0; // tipo

buf tra[1] = 1; // num. byte

buf tra[2] = 0; \} // byte testo

byte = SOH;

scrivi thr (byte);

stato \overline{t} = S1;

break;

case S1: // trasmette progressivo trasmesso locale

cks t = 0; // azzera checksum

// indice buffer a inizio

it = 0:

byte = prog t 1;

scrivi thr (byte);

cks t += bvte;

stato t = S2;

break;

case S2: // trasmette progressivo ricevuto locale

byte = prog r 1;

scrivi thr (byte);

cks t += bvte;

stato t = S3;

break;

```

```

case S3: // scrive codice tipo

byte = buf tra [it];

scrivi thr (byte);

it++;

cks t += byte;

stato t = S4;

break;

case S4: // trasmette numero byte testo (>=1)

byte = buf tra [it];

scrivi thr (byte);

it++;

count = byte;

cks t += byte;

stato t = S5;

break;

case S5: // trasmette i byte del testo

byte = buf tra [it];

scrivi thr (byte);

it++;

cks t += byte;

if (--count == 0)

stato t = S6;

break:

case S6: // trasmette byte di checksum

byte = cks t;

scrivi thr (byte);

stato t = S7;

break;

case S7: // termine trasmissione

disab tra ();

enab ric ();

stato t = S0;

break;

69

```

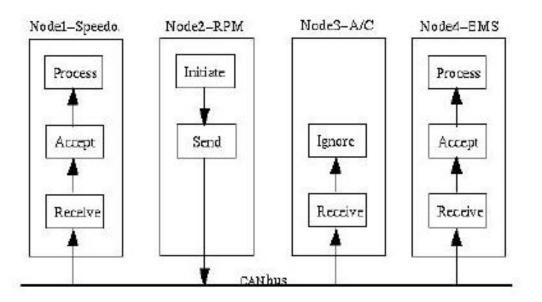

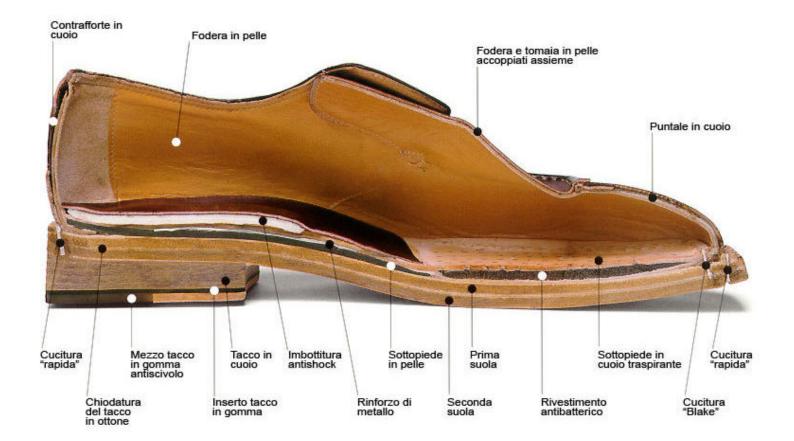

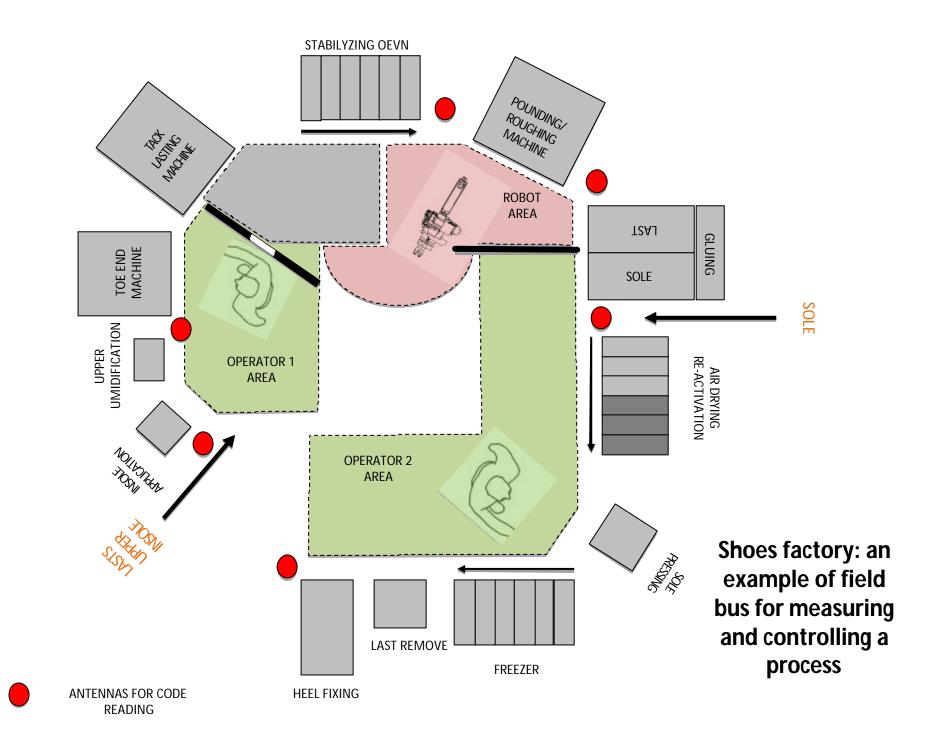

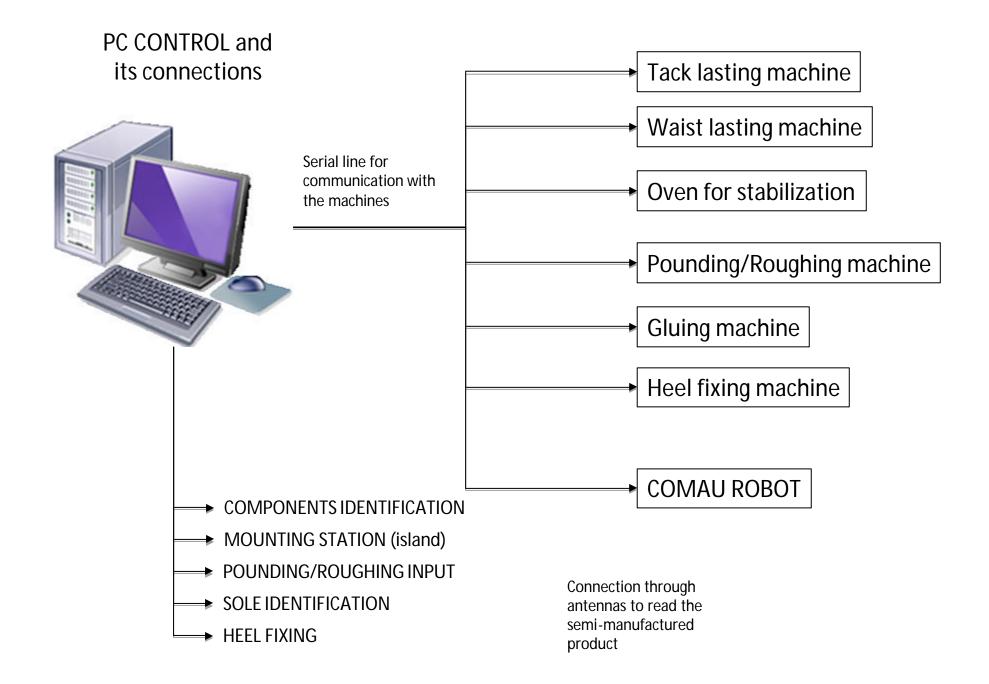

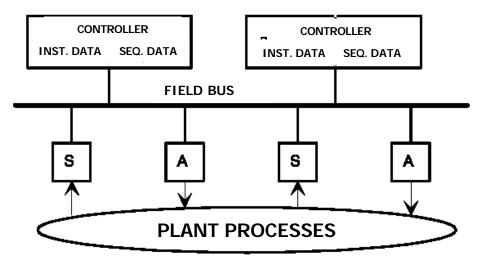

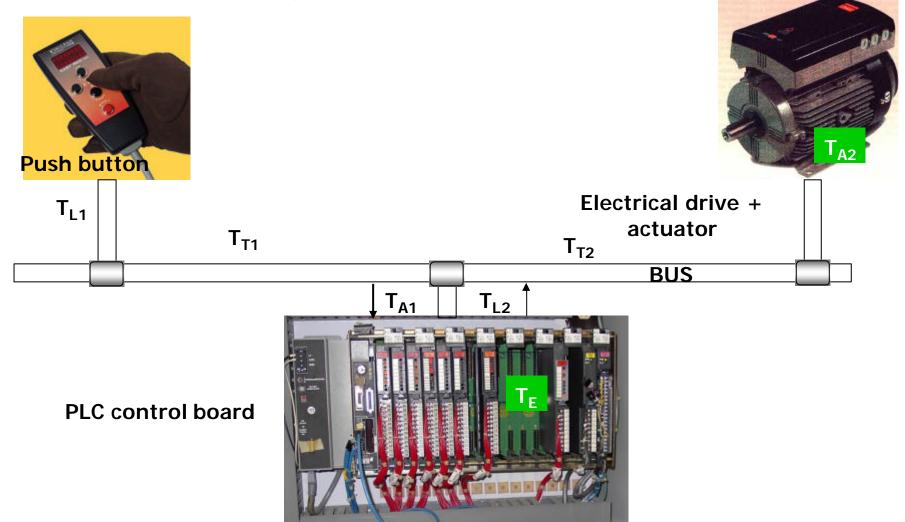

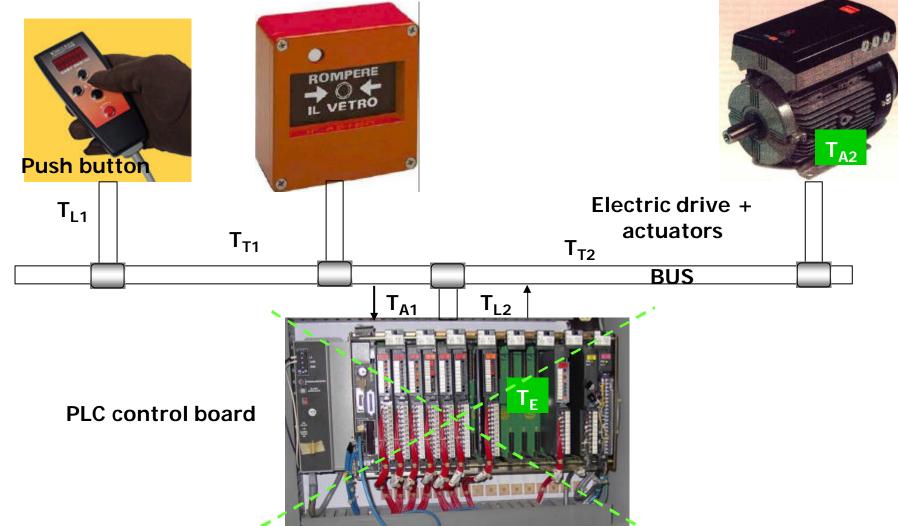

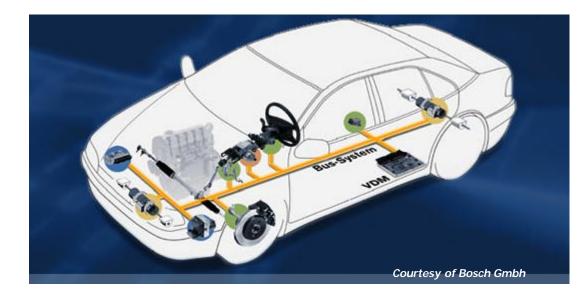

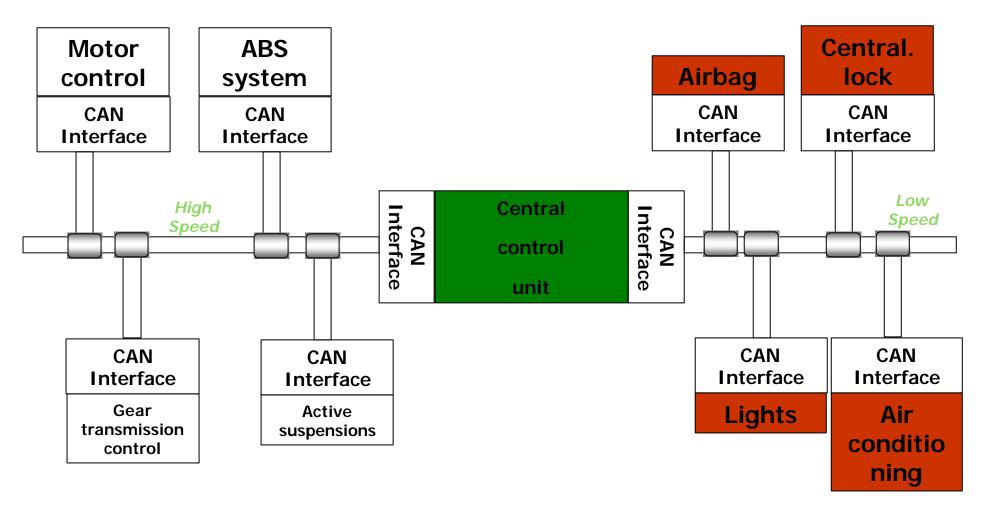

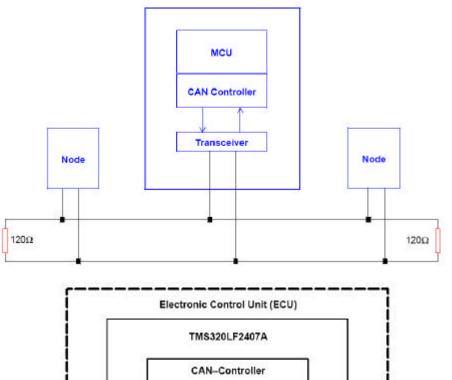

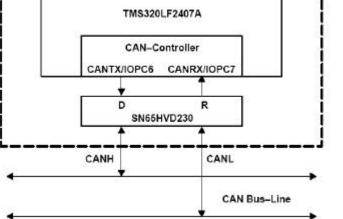

### **FIELD BUS – A typical application**

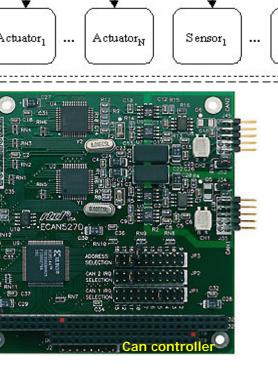

## **Field Bus**

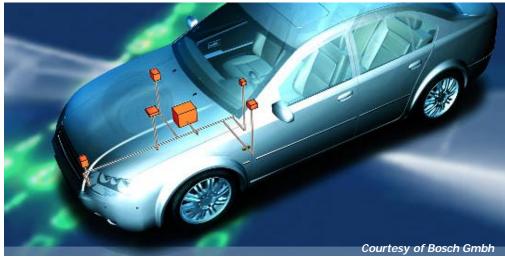

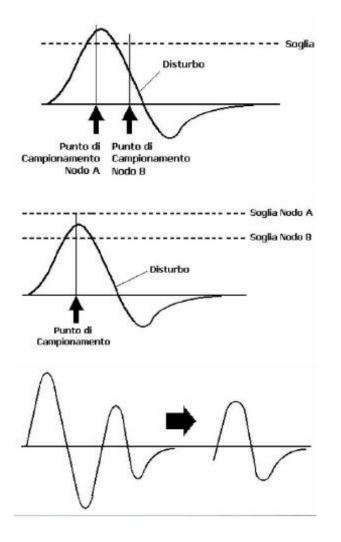

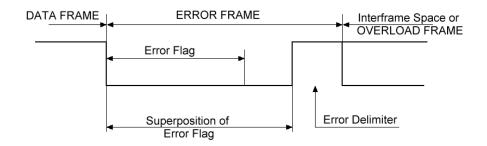

Standardization of communications between devices used in data acquisition and industrial process control.

Two possibilities: industrial networks and field buses

•Networks (Ethernet) diffused and popular. Faster, wider, more expensive than field buses

•Field buses (Can) good compromise among performance, real time, robustness, costs

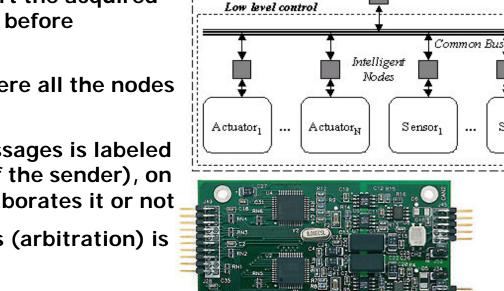

A field bus is a distributed control system made up by one or more controllers, sensors and actuators

Data are "logically divided" in controllers:

• "process data base": status process variables, periodically refreshed through instantaneous sensor measurements

• "historical data base" with significant events organized in queues (sequential)

## **Required services**

periodic communication of sensor acquisitions and command towards the actuator aperiodic communication with high priority of events (alarms, anomalies, ...) aperiodic communication of low priority infos (configurations, on line diagnostics)

### **Constraints (specs)**

Instantaneous data refresh frequency = sensor sampling frequency

Time validity of values = consider that the physical distance between producer and consumer implies a delay that does not compromise the system stability