### **INDUSTRIAL INFORMATICS**

### and EMBEDDED SYSTEMS

Francesco Leporati

Tel. 0382 985678 e-mail: francesco.leporati@unipv.it

1

University of Pavia - Francesco Leporati – Industrial Informatics and Embedded Systems 2018

### THE COURSE

**Issues:** requirements of embedded systems in typical industrial applications together with corresponding digital communication techniques for acquisition from sensors and motor driving

Program:Data acquisition (analog and digital interfacing), chap. 7 e 8 handouts + slidesNumerical filters – chap. 8 handouts + slidesIndustrial communication protocols (typical standards for serial and parallelcommunication + field buses) - chap. 9-14 handouts + slidesEmbedded Systems: typical elaboration architectures: Arm 7; low powerdevices : slides

Material: handouts + lessons slides + lecture notes

**<u>Requirements</u>**: Computer Architectures, Electronics, Industrial Electronics, Networks

**Time table:** Thursday 11-13 & 14-16 rooms E8-E1 Thursday 14-16 room E4 Friday 9-11 room E2

**Reception:** Wednesday and Thursday 17-18

### **Companies that are looking for students:**

MARELLI MOTORSPORTS (Corbetta Milano): video data logging, telemetry

TEMIS (Corbetta Milano): automotive, satellites, data acquisition and communication

BDSOUND (Assago): *sound engineering*, audio signals acquisition through microcontrollers (Cortex M4, ST, ...)

AZCOM (Rozzano):wireless (and not) safe communications through sw control (DSP and FPGA processors)

MULTIPROTEXION: mobile videosurveillance for trucks, cars, commercial vehicles, containers, ...

### **MASTER THESIS (in laboratory)**

#### DSP, GPU, FPGA technologies applied to:

Brain cerebellar simulation/emulation

Hyperspectral image processing for high accuracy cancer detection

Classification with concurrent neural networks

Super-resolution data fusion

#### Master degree presentation:

March 15th Thursday 14-16

University of Pavia - Francesco Leporati – Industrial Informatics and Embedded Systems 2018

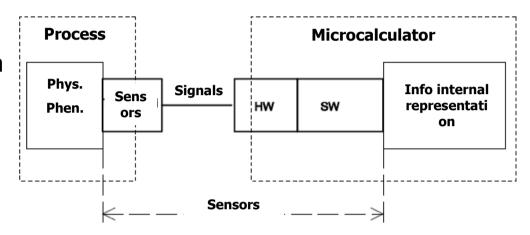

**Interfacing** = interactions between active function devices (i. e. CPU) and/or passive ones (i. e. memories, sensors, ports)

The course is mainly (but not only) focused on the interactions between **calculator** and **external world** (every thing not directly manageable by the CPU through buses)

Several kinds of **in-homogeneities**:

- *Physical*: the external world is characterized by physical parameters that can be represented only through electric entities with suitable amplitudes (transducers)

- Formal: codification (BCD/Gray), representation (pulse count or frequency measurement), signal processing/management (modulation)

- *Temporal*: how external phenomena are synchronized with signal acquisition/emission? (circuits, interrupt/polling/DMA, real time protocols)

- *Spatial*: computers and controlled devices are not physically adjacent (**transmission**)

- Attitudinal: Human Computer Interaction

A suitable **chain** of interacting devices allows to overtake these in-homogeneities

#### **Typical computer-external world interfacing**

**Interface design** = identification of a chain of components able to wholly satisfy the requirements of data transformation and communication

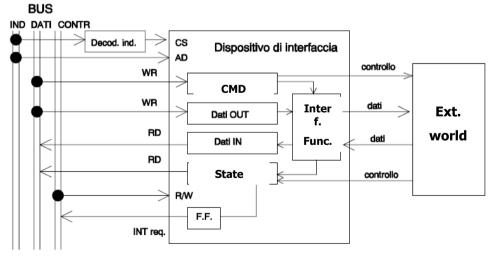

#### A general interface digital circuit

•I/O buffer (Fifo)

• *State registers* for significant situations (errors, overrun, interrupt ...)

• *Command registers* to setup mode functions and modify state bits

• Various functions: DMA, ser/par transfers

University of Pavia - Francesco Leporati - Industrial Informatics and Embedded Systems 2018

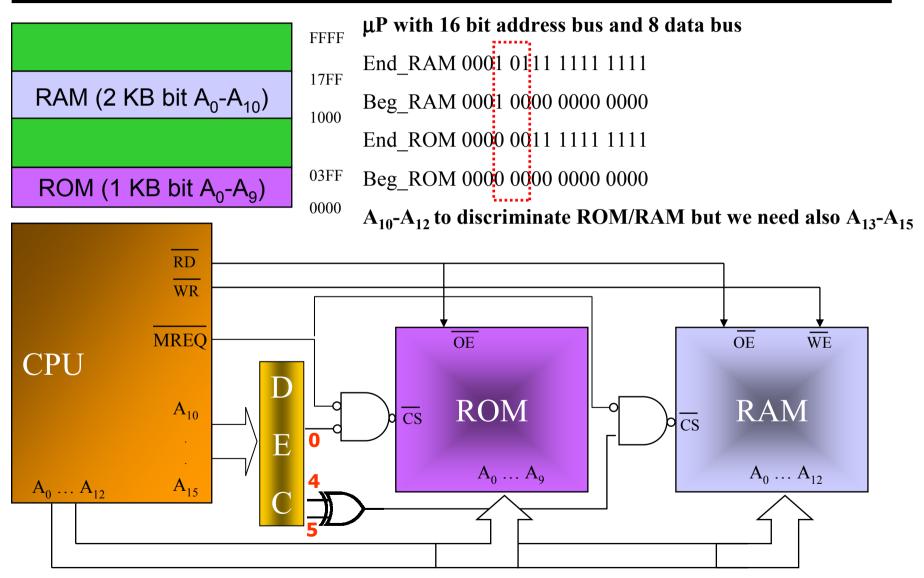

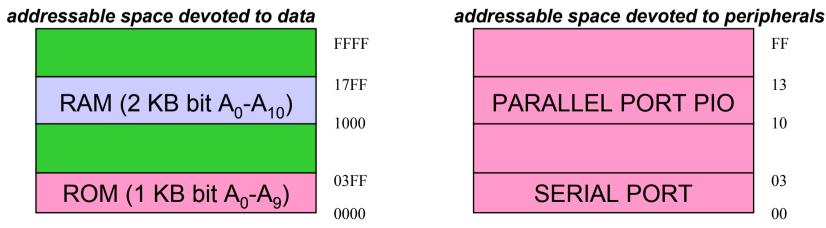

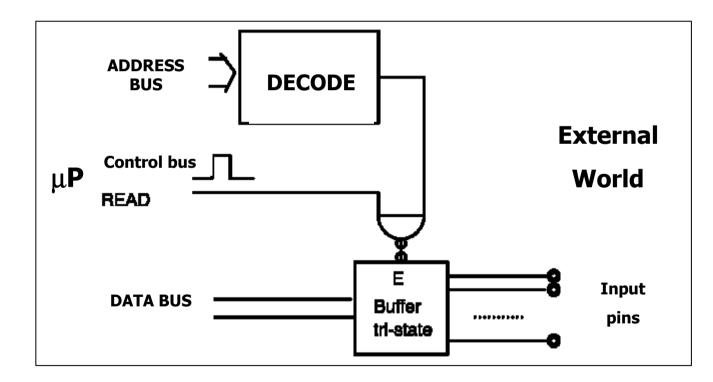

### ADDRESSING ON THE BASIS OF A MEMORY MAP

### ADDRESSING ON THE BASIS OF A MEMORY MAP

#### 0x200F 1) A single address space (MEMORY MAPPED I/O) RAM I/O device lw \$req1, off(\$req) \$reg= port (mem) address 0x202F bytes I/O Ports Assigned ex. ARM, MIPS Addressing 0x200F Space 2) Double address space (CUSTOM INSTRUCTIONS) 0x2000 I/O device bytes 0x2003 \$reg1, off(\$reg) \$reg=memory address lw Data register I/O device RAM Data Register \$dest, (\$reg) \$req=port address in bytes 0x2000 ex. INTEL

Control signals to distinguish between memory and I/O access (MREQ, IORQ)

9

University of Pavia - Francesco Leporati - Industrial Informatics and Embedded Systems 2018

### **On off signals**

•They represent physical entities acquired through single bits of a microprocessor port

•What is important is the value of the bit, not its variation

•8-16-32 bit groups acquisition (bytes, words)

•Let's **test** the Kth bit

```

Esempio in C

var_bool = 0;

if (immagine & mask_K)

var_bool = 1;

Variante più compatta:

var_bool = (immagine & mask_K) && TRUE;

```

#### •And now two assembly routines (the right one is optimized)

| Esempio in Assembler 8086 (versione intuitiva)<br>MOV AL, [IMMAGINE]<br>AND AL, MASK_K<br>MOV [VAR_BOOL], AL<br>JZ SKIP<br>MOV [VAR_BOOL], 0FFH<br>SKIP: | Esempio in Assembler 8086 (versione più efficiente da meditare)<br>MOV AL, [IMMAGINE]<br>AND AL, MASK_K<br>SUB AL, MASK_K<br>SBB AL,AL ; SuBtract with Borrow<br>CPL AL<br>MOV [VAR_BOOL], AL<br>seguito |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

#### **On off signals**

•Let's **set** the Kth bit

```

Esempio in C

if (var_bool)

immagine |= mask_K; // OR con mask

else

immagine &= ~ mask_K; // AND con COMPLEMENTO di mask

```

| Esempio in As | sembler        |                                      |

|---------------|----------------|--------------------------------------|

| •             | AL, MASK_K     | ; maschera                           |

| AND           | AL, [VAR_BOOL] | ; isola bit in posizione K           |

| MOV           | AH, AL         | ; salva in AH                        |

| MOV           | AL, MASK_K     |                                      |

| CPL           | AL             | ; maschera complementata             |

| AND           | AL, [IMMAGINE] | ; azzera bit in posizione K          |

|               | AL, AH         | ; inserisce nuovo bit in posizione K |

|               | [IMMAGINE], AL | , aggiorna variabile immagine        |

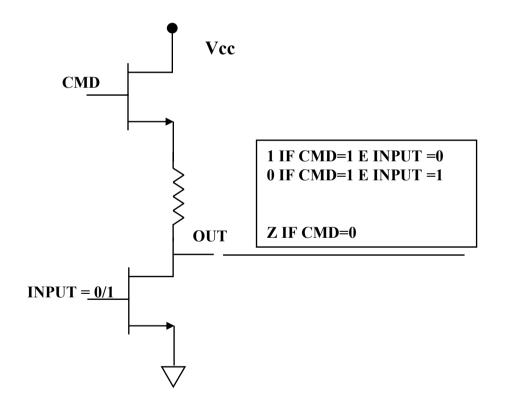

#### **On off signals: "state" acquisition**

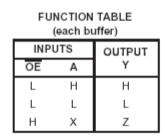

• The value of a bit is read to establish the level (*state*) of a line related to a physical entity: use of a *three state buffer*

#### **On off signals**

• three state buffers to de-couple the line with respect other devices

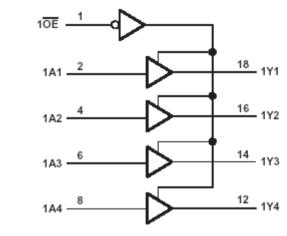

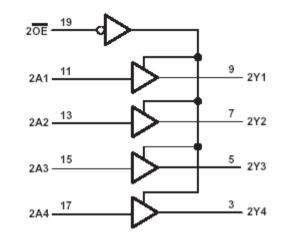

#### **COTS buffer components (Texas Instr. SN 74AC244)**

| 10E                                |     | U 20 | V <sub>CC</sub> |  |  |  |

|------------------------------------|-----|------|-----------------|--|--|--|

| 1A1                                | 2   |      | 20E             |  |  |  |

| 2Y4                                |     | 18   | 1Y1             |  |  |  |

| 1A2                                |     |      | 2A4             |  |  |  |

| 2Y3                                | 5   | 16   | 1Y2             |  |  |  |

| 1A3                                | 6   | 15   | 2A3             |  |  |  |

| 2Y2                                | 7   | 14   | 1Y3             |  |  |  |

| 1A4                                | 8   | 13   | 242             |  |  |  |

| 2Y1                                | 9   | 12   | 1Y4             |  |  |  |

| GND                                | 10  | 11   | 2A1             |  |  |  |

|                                    | _   |      | 1               |  |  |  |

| SNEAAC                             | 244 | EV E |                 |  |  |  |

| SN54AC244 FK PACKAGE<br>(TOP VIEW) |     |      |                 |  |  |  |

|                                    |     |      |                 |  |  |  |

| 20EC                               |     |      |                 |  |  |  |

|                                    | ~ ~ |      |                 |  |  |  |

| . f. 1                             | 32  | 1 20 | 19              |  |  |  |

1A2

2Y3

1A3

2Y2

1A4

5

6

Π8

9

10 11 12 13

2Y1 GND 2A1 1Y4 2A2

.

,

logic diagram (positive logic)

#### University of Pavia - Francesco Leporati – Industrial Informatics and Embedded Systems 2018

1Y1

2A4

1Y2

2A3

1Y3

17 E

16

14

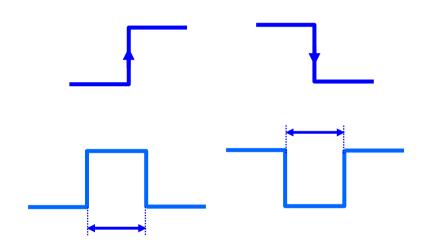

#### **On off signals: event triggering**

•The value of a bit is read just to establish if a commutation has occurred (event) of a line related to a physical situation, by comparing it with the previous value

•2 possible approaches:

#### -SW triggering through polling

>A microprocessor port is continuously sampled. The software application compares the new value with the old one and identifies the eventual commutation

#### -triggering through interrupt

- >The signal carrying the "event" is connected to a microprocessor port's pin

- >The single commutation edge is determined through pins edge triggering (falling/raising edges)

- >Both the edges are acquired through suitable electronic circuits sensible to edge or to levels. Where is the difference?

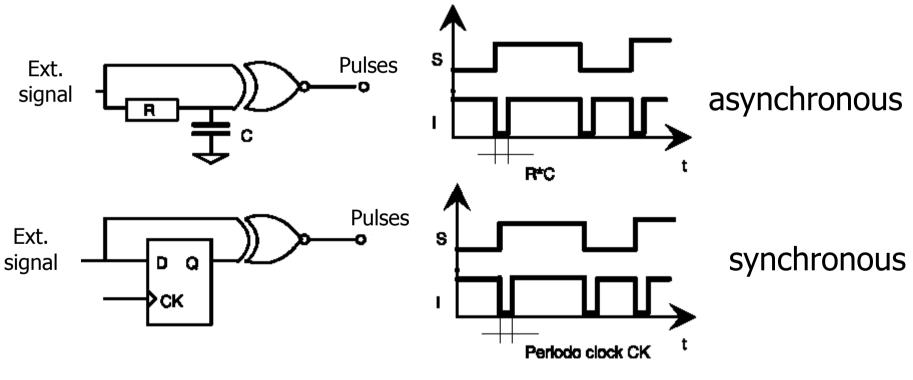

#### **On off signals: "event" acquisition through interrupt**

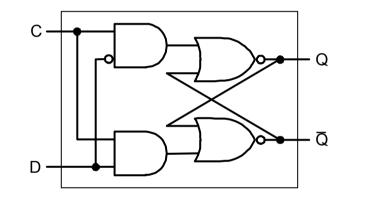

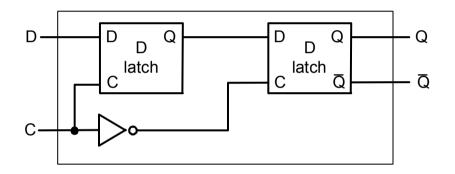

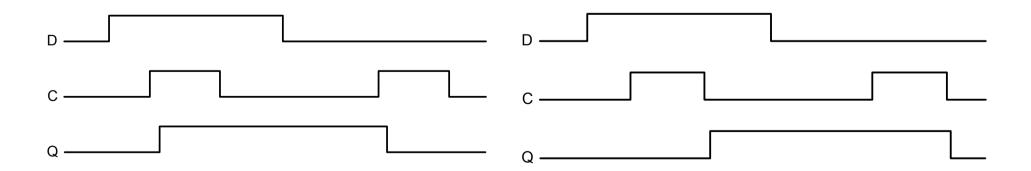

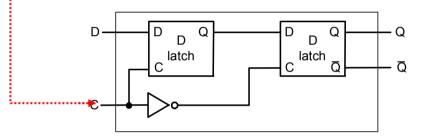

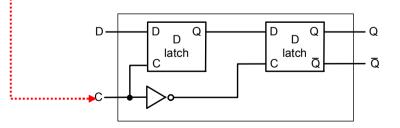

Latch (sensible to the level)

FF (sensible to the edge)

University of Pavia - Francesco Leporati – Industrial Informatics and Embedded Systems 2018

#### **On off signals**

• a bit value is read to establish the possible commutation using *one-edge sensible circuits*. Below a circuit able to transform commutation of **both** the edges in a single direction

$T_{ck} < T_s/2$  if duty cycle 50%

University of Pavia - Francesco Leporati - Industrial Informatics and Embedded Systems 2018

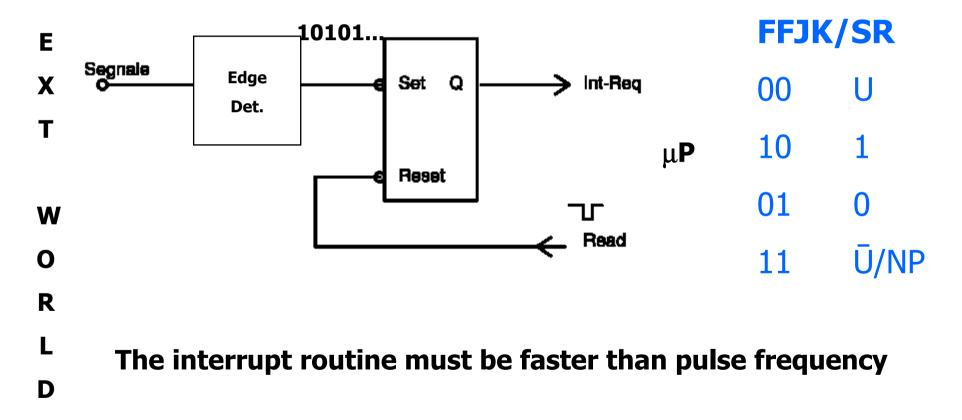

#### **On off signals**

a bit value is read to establish the possible commutation using *level sensible circuits* (a FFJK, or a SR, is required to keep the input fixed)

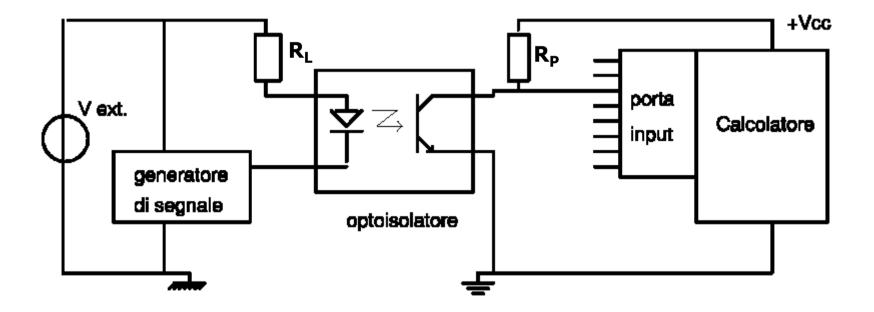

#### **Physical signal adjustment: opto-couplers**

- •Mandatory if grounds are different or if possible over-voltages

- $\bullet R_L$  to determine necessary current for LED power up

- •R<sub>P</sub> pull-up (saturation vs "steep" edges: what possible values?)

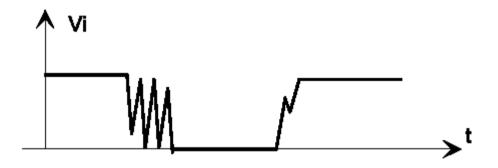

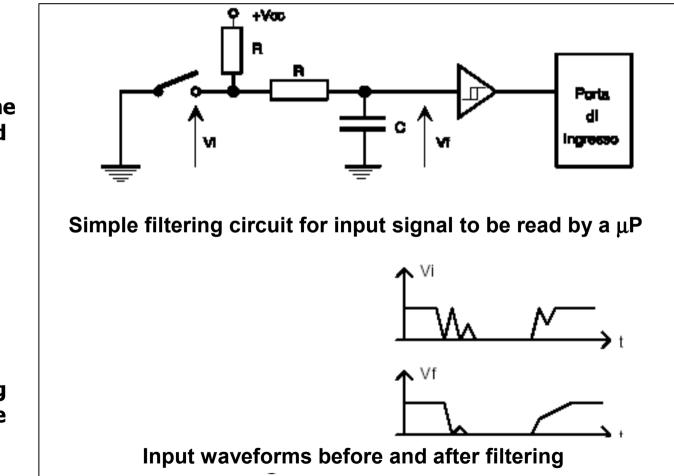

#### On off signals

•This kind of signals are produced by relays, electronic switches, buttons, limit-switches

•Possible *spurious* states irrelevant if the signal level is required but misleading if we are interested in the commutation (i. e. an associated *event*)

•electric vs algorithmic filtering

*–electric*: required if interrupt o counters are used ( $\Rightarrow$  RC + Schmitt trigger)

*–algorithmic*: necessary if the signal is sampled. The sampling will turn out in a series of values among which some are significant others not (spurious). The choice among them is driven by the information that the signal carries  $\Rightarrow$  definition of a suitable *transient death time*

University of Pavia - Francesco Leporati – Industrial Informatics and Embedded Systems 2018

#### Fine corsa a leva, stelo, pulsante

#### Lever, stem, push-button,

#### Fine corsa ad albero

#### tree limit switches

Anello di tenuta ermetica a tre vie per l'albero in fluoroelastomero brevettato da Allen-Bradley rinforzato per sopportare lavaggio con getto in pressione fino a 83 bar (8.270 kPa)

La guarnizione a diaframma a tenuta stagna fra la testa operatrice e il corpo del fine corsa offre ulteriore protezione contro agenti contaminanti quanto la testa operatrice viene rimossa

In grado di sopportare immersione in condizioni che superano i requisiti NEMA 6P

#### **Electric filter through RC circuit + Schmitt trigger**

Choose carefully the values of R and C, since they influence the circuit time constant and thus the reliability of the read from the microprocessor

Slow capacitor charge/discharge could imply a slow crossing in the uncertainty range, bringing a oscillating behaviour. Therefore a Schmitt trigger could be suitable.

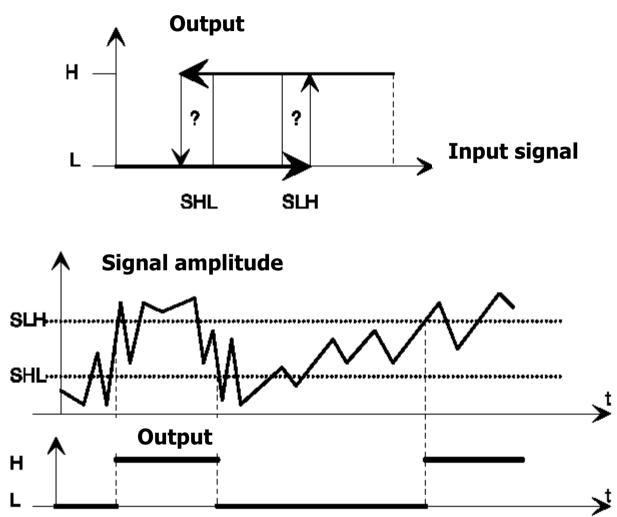

#### **Schmitt Trigger (Filter)**

- •Its characteristic is an hysteresis

- •It depends on the behavior of a magnitude (memory effect)

- •Useful in case of slow spurious signals and hw detection of a commutation

- •The input signal is "squared" and is more suitably distinguished by the port electronic circuits

University of Pavia - Francesco Leporati – Industrial Informatics and Embedded Systems 2018

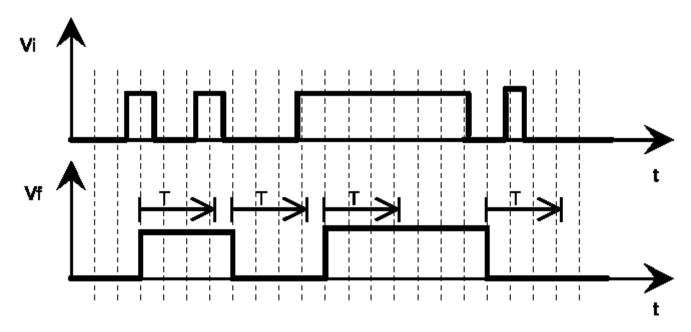

### **Algorithmic filtering: first edge detection**

- •The first variation is considered as really significant and accepted

- •Further variations are ignored during the time interval T (*transition death or dead time*)

- •The algorithm does not work with isolated spurious signals

- •Spurious signals follow a real significant event and run out within the T interval. Ok in case of mechanical contacts

University of Pavia - Francesco Leporati – Industrial Informatics and Embedded Systems 2018

#### First edge detection, a simple assembly code

; Routine da chiamare ciclicamente ad ogni periodo di campionamento. ; Riporta in AL il valore filtrato ACQ BIT N: CMP [TRANSITORIO].0 JE REGIME ;qui in transitorio - conta il tempo trascorso DEC [TRANSITORIO] JMP ESCI ;qui transitorio esaurito - pronto a sentire event. commutaz. REGIME: AL.PORTA IN IN ;legge la porta AND AL.MASK N isola il bit considerato: CMP AL, [PRECEDENTE] confronta con valore preced. JE ESCI ;qui rilevata commutazione MOV [PRECEDENTE].AL ;aggiorna il valore MOV [TRANSITORIO],T MORTO rilancia il transitorio: ESCI: AL.[PRECEDENTE] MOV riporta il valore valido; RET

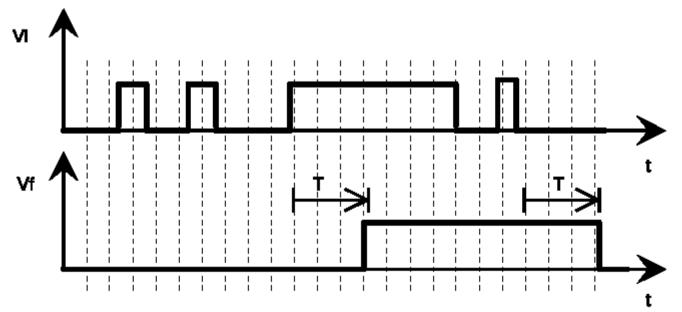

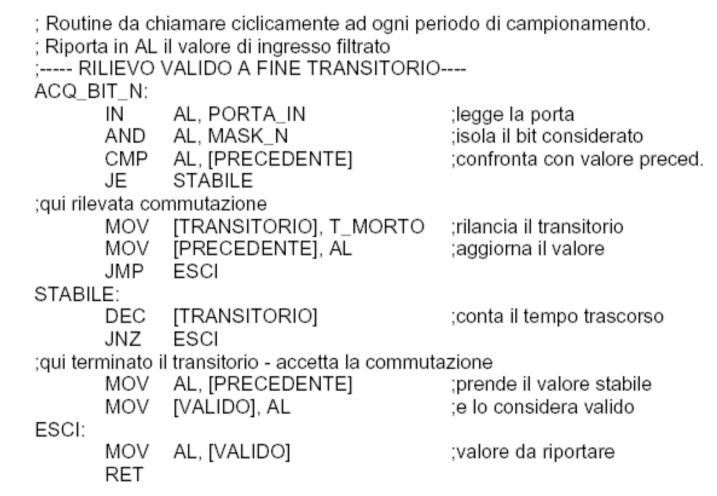

#### **Algorithmic filtering: expired transient detection**

- •The first variation is not significant

- •The corresponding state is accepted as valid only if unchanged within T time interval

- •The algorithm works well with isolated spurious signals

- •A low pass filtering effect (delay)

#### **Exhausted transient detection, a simple assembly code**

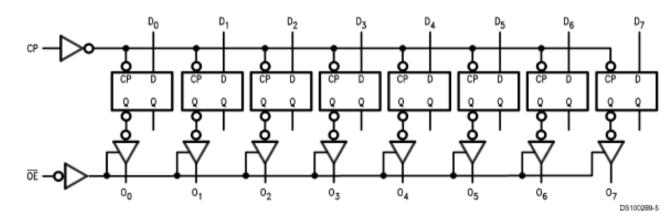

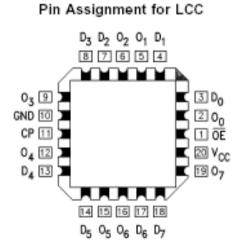

#### **On off signals emission**

- •The output on a  $\mu$ P port is carried out through latches (permanent values)

- •Output of initial setup values or after a reset (0 if possible)

- •Output through "image" variables (it is not possible to output single bits)

- •Image variables processed through AND/OR/XOR masks

- •the National Instruments Latch 54ACT374 component

Logic Diagram

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays.

#### Truth Table

| Inputs |    | Outputs |    |

|--------|----|---------|----|

| Dn     | CP | OE      | On |

| Н      | ~  | L       | Н  |

| L      | ~  | L       | L  |

| х      | х  | Н       | Z  |

H = HIGH Voltage Level L = LOW Voltage Level X = Immaterial Z = High Impedance

EOW-to-HIGH Transition

#### Latch 54ACT374

#### **National Instruments**

University of Pavia - Francesco Leporati – Industrial Informatics and Embedded Systems 2018

**Pulses**

#### **Pulses can be acquired for:**

- Temporization

- •Counting a suitable number of moving objects

- Calculating object position

- Calculating object velocity

Binary digital signal commutations to which a single event is associated considered as significant

Sometimes both the edges are useful since associated to the beginning and the end of a event  $\Rightarrow$ interval measurement

#### Pulses can be emitted for:

- •PFM device driving

- •PWM device driving

- •Power supply to an electric load through partialization of the signal

#### **Pulse acquisition for counting (object passage, complete rounds ...)**

- •LED + phototransistor to reveal the object passage

- •Total primary counter must be upgraded (i. e. program variable)

- •Max reachable value => type definition => unsigned long (32 bit)

- •Non volatile counting (eventually secondary counters in powered buffer memories / files. Trade-off between freshness and CPU overload)

- Manual vs automatic reset operations

Variables must be stored through atomic saving operations in memory

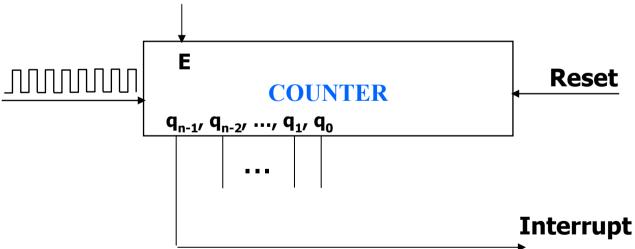

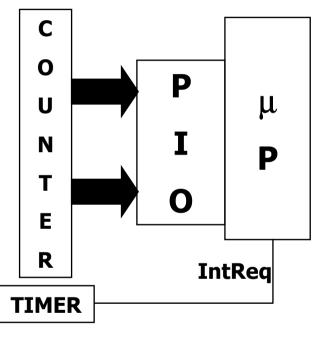

#### Hw primary counter

- •Less sw elaboration charge onto the CPU

- •Mandatory if pulse frequency not acquirable through polling from the  $\mu$ P port (it requires few assembly instructions)

- If the counter is connected with a  $\mu\text{P}$  port we read a state information

- •If the counter is connected with an interrupt line (triggers the interrupt) we read an event information

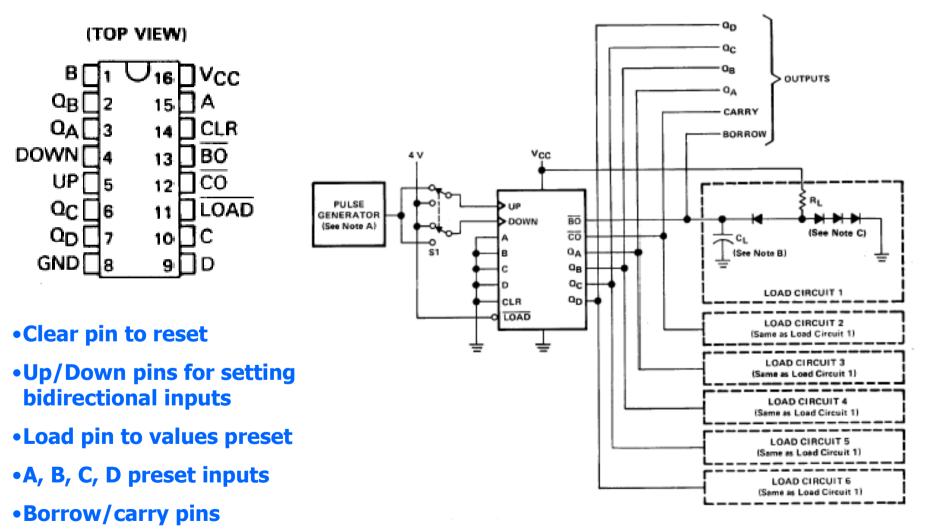

#### Hw primary counter: a commercial component Texas SN74193

#### External (primary) hw counter providing a "status" information

N bit hw counter

•  $\mu$ processor port connection

•Acquisition routine periodic activation  $T_c$

where  $T_c \leq (2^{N-1})*T_{imp}$

```

AGGIORNA CONTATORE:

Input from the port (present counter

SUB AX,AX

value)

IN

AL, PORTA CONT

# pulses between two inputs (V<sub>new</sub> - V<sub>old</sub>

SUB AL, [PRECEDENTE]

[PRECEDENTE], AL

ADD

added to a total (secondary) counter

ADD

[CONTATORE], AX

(carry management)

[CONTATORE + 2],0

ADC

RET

```

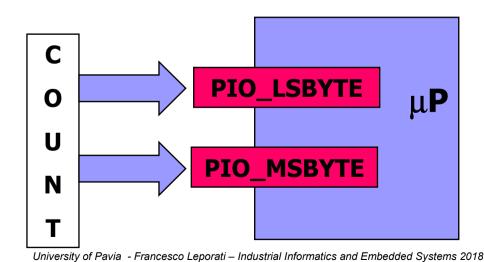

### External (primary) hw counter providing a "status" information

- If n° of bits > than readable by a single instruction

- •Bytes from the counter are read with successive read phases

- •Auxiliary register with the same width of the counter to be read in two phases

AGGIORNA CONTATORE: AL.P MSBYTE IN RIPETI: MOV BH.AL IN AL.P LSBYTE MOV BL.AL IN AL.P MSBYTE CMP AL.BH JNE RIPETI ;qui BX = valore valido MOV AX.BX SUB AX.[PRECEDENTE] ADD [PRECEDENTE].AX ADD [CONTATORE].AX ADC [CONTATORE + 2],0

#### External (primary) hw counter providing an "event" information

Interrupt line connected to a single counter bit or to the carry bit

Used as "pre-scaler" (frequency division)

$F_{out} = F_{in} / 2^{N} (if carry set)$  $F_{out} = F_{in} / 2^{k} (if k^{th} bit connected)$

Memory SW counter upgrading (if high frequencies)

Least significant count directly read from the counter

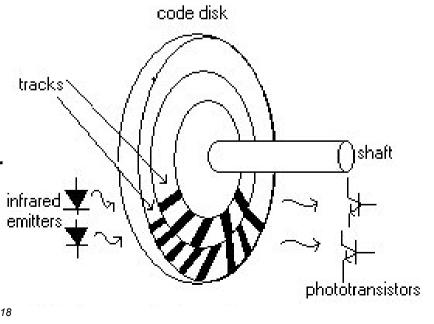

#### **Pulses to evaluate an object position**

•Pulses corresponds to incremental movements. Where is the "zero" point?

**Signed numbers**

-Is it a un-surmountable extreme? Unsigned numbers

-Is it an arbitrary position?

•The incremental encoder

A wheel made up by windows alternatively transparent and opaque to a light beam emitted by a LED source

The light is received by a phototransistor

Each windows provides a binary information (i. e. a bit)

#### **Incremental Encoder**

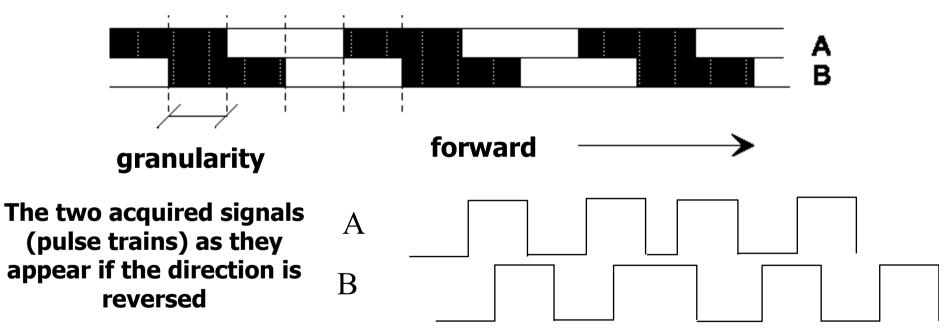

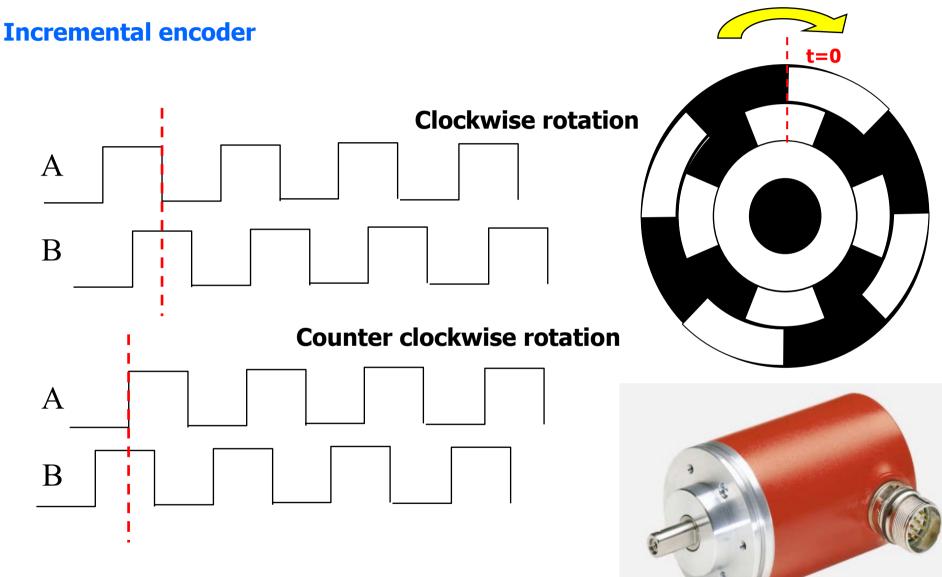

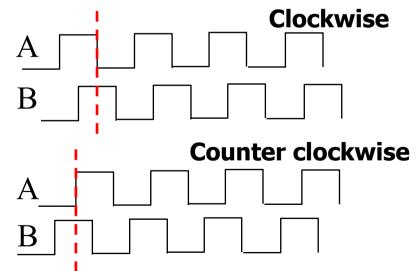

- •Two concentric crowns, 1/4 period out of phase

- •Two couples of LED/transistor (1 light, 0 dark).

•Minimum measurable angle = half window

#### **Counting specs**

- definition of "zero" (natural/integer counting variable)

- maximum counting vs granularity (size)

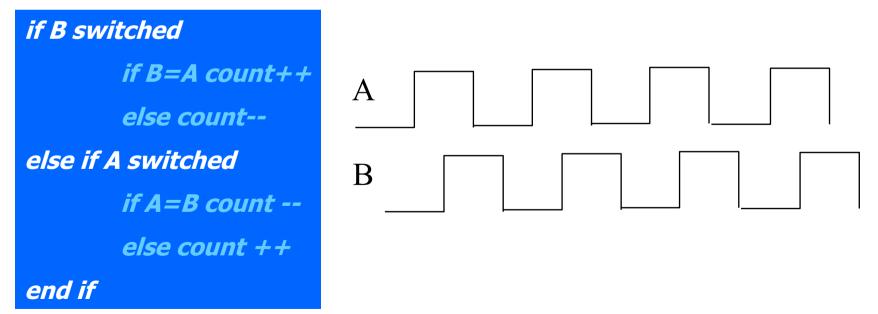

#### Counting

- edge detection

- movement direction

- primary counter upgrading (then eventually upgrade the secondary one)

- 2 possible approaches: sw/hw

| Α | В | С   |

|---|---|-----|

| Р | 0 | + 1 |

| Р | 1 | - 1 |

| Ν | 0 | - 1 |

| Ν | 1 | + 1 |

| 0 | Р | - 1 |

| 1 | Р | + 1 |

| 0 | N | + 1 |

| 1 | N | - 1 |

- •A and B: 2 pulse trains connected to two pins of the  $\mu$ P port

- Commutations detection

- Movement direction identification: forward (+) or backward (-)

- •Counter variables (primary and eventually secondary)

- algorithm (hypothesis clockwise rotation considered as positive)

#### An example of sw management of a bi-directional incremental encoder

AGGIORNA POS ENCODER: AL,P\_ENC IN AND AL.3 MOV BL.AL SHR BL.1 XCHG AL.[PRECEDENTE] XOR AL, [PRECEDENTE] ESCI JΖ ;qui rilevata una commutazione AND AL.1 MOV CL.AL MOV AL.[PRECEDENTE] AND AL.1 XOR AL.BL XOR AL.CL DECREMENTA JNZ ;qui si deve incrementare [CONTATORE],1 ADD JMP ESCI DECREMENTA: SUB [CONTATORE],1 ESCI: RET

;maschera i bit utili

;BL.0 = B (porta segnale B in bit (

;CL.0 = 1 se commutato A

;AL.0 = A

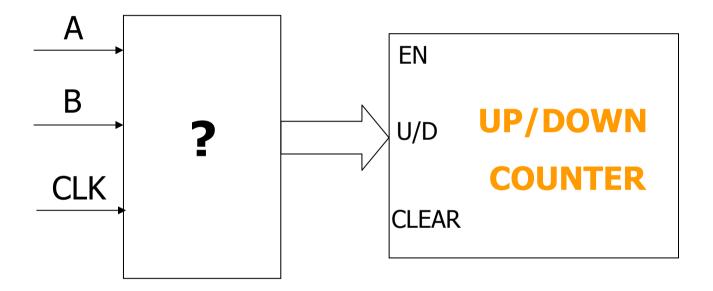

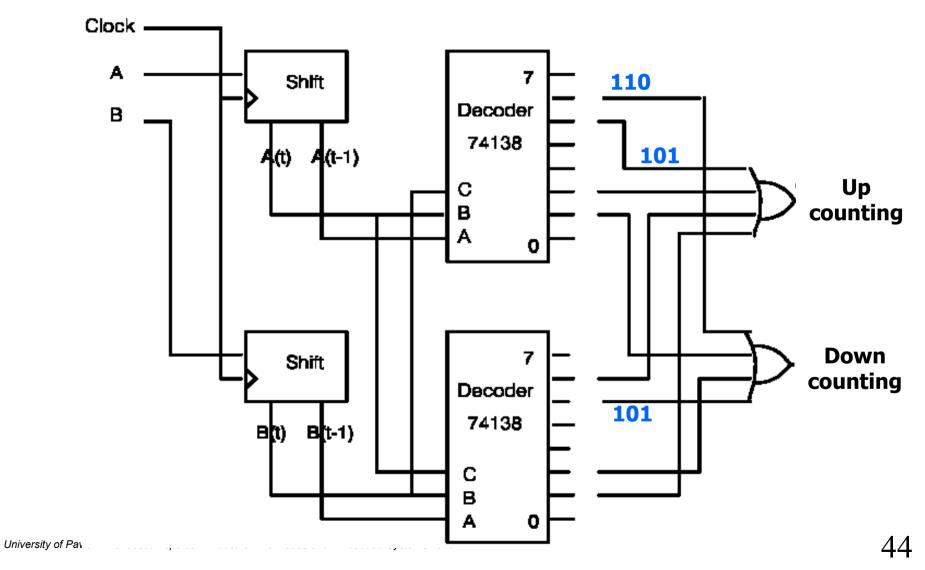

#### Hw management of a bi-directional incremental encoder

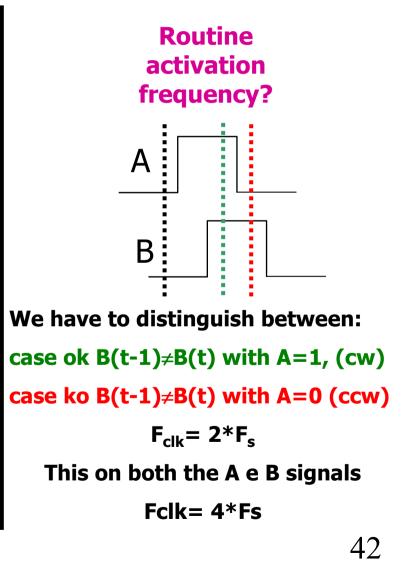

Activation frequency?

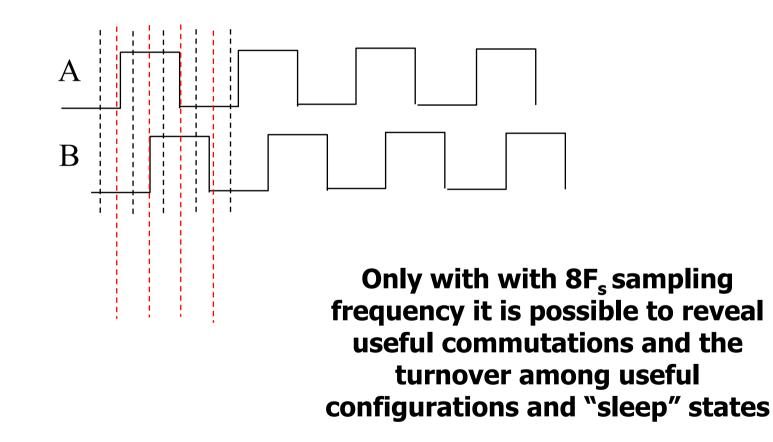

The hw logic must distinguish among commutations of the same signal (A o B); however, within the present commutation and the next one it must also recognise if the other signal is 0 or 1.

$$F_{clk} = 8 * F_s$$

#### Hw management of a bi-directional incremental encoder

#### Hw management of a bi-directional incremental encoder

#### **Pulses for timing**

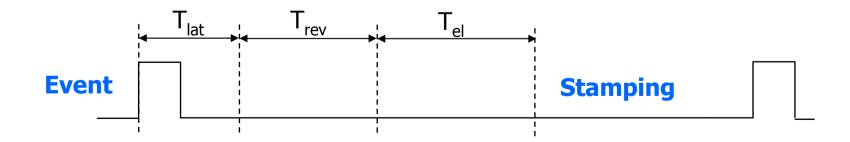

Time-stamping means to associate events and times into which they happen

*Errors* due to the model describing time evolution within the machine (TIG – temporal granularity)

*Delays* due to timer acquisition sw  $(T_{el})$  and to event recognition  $(T_{rev})$

*Latencies* = time interval between the event and its perception  $(T_{lat})$ . Non deterministic, if they are due to resources charged with task perception and in that moment devoted to other activities (priority). Typical in interrupt service and in processes activation

#### **Pulses for timing (maximum priority routine)**

Events internal to the machine (i. e. switch of a control unit signal)

```

t-TIG+T_{el} < T_{st} < t+T_{el}

```

Events external to the machine (i. e. switch of a signal read through a port)

$$t-TIG+T_{rev}+T_{el} < T_{st} < t+T_{lat.max}+T_{el}+T_{rev}$$

Measurement of an interval between external events (constants components neutralise each other, deterministic ones do not disappear)

$$-TIG-T_{lat.max} < (T_{st1}-T_{st2}) < TIG+T_{lat.max}$$

### What is TIG? It depends on the machine time representation model. Let us open a parenthesis ...

### TIME CHARACTERISATION

- Is the time an event container (box) or the events cause the course of the time?

- During life we follow the first approach, in computer science we are close to the second one

- CLOCKS = phenomena that generate regular events (ticks) used to quantify the time passing

- We need a model

# TIME AS IT IS REPRESENTED WITHIN A CPU

- •Hp: bijective correspondence among time moments and real numbers

- •Continuity, limit, derivative, integral existence ecc.

- •Time as linear, monotonic, discrete

- •Clock = time events generator with domain N<sup>+</sup>

- •Quantization = duration of the phenomenon taken as clock, usually very negligible with respect events that must be measured

# TIMING MODEL

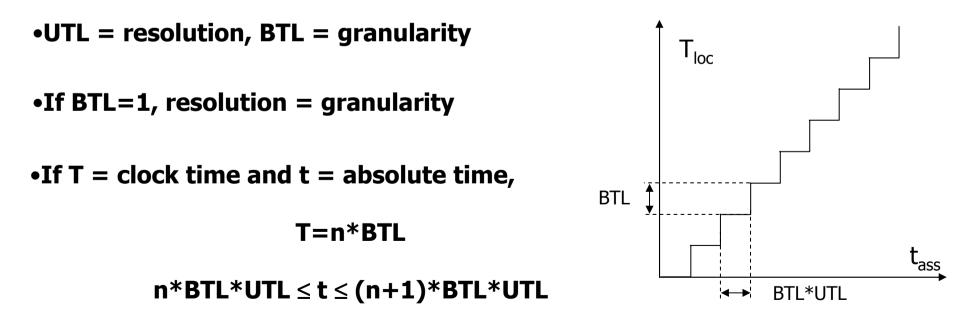

•LOCAL TIME UNIT (UTL) = absolute time interval corresponding to 1 in the measurement unit of the clock

•LOCAL TIME BASE (BTL) = multiple of the UTL, representing the period of the cyclic phenomenon assumed as clock

•Let' suppose that in a PC the real time clock is 55 msec: the time is represented in msec (UTL), but it is increased every 55 (BTL)

# TIME MODEL: PRECISION ERRORS

•They are due to how the phenomenon (assumed as clock) differs from the ideal behavior

#### •PRECISION

A clock is precise if t(tick(n)) - t(tick(n-1)) = BTL\*utl + e(n) with e(n)=0

– Systematic error  $\Rightarrow$  the phenomenon taken as clock features a not correct frequency

- Null mean errors  $\Rightarrow$  not stable frequency (jitter)

- precision measurement = BTL\*utl /mean\_err = (10<sup>4</sup>-10<sup>6</sup>)

#### •CORRECTNESS

A clock is correct if abs(T-t/UTL) < BTL, that is the local time T is synchronised with the absolute time (within the quantization error BTL)

-A precise clock if is correct in t, is correct in t'>t

-Sistematic unaccuracy (mean\_err $\neq$ 0)  $\Rightarrow$  no correctness

-If intervals are measured, systematic errors do not exert any influence

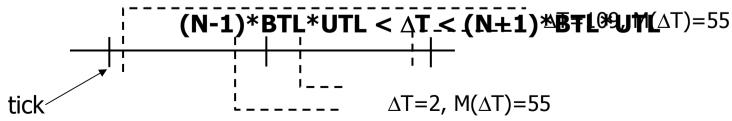

# TIME MODEL: QUANTIZATION ERRORS

•They are caused by the representation of the time

•ORDER: it si not possible to establish an order between 2 events that happen within 2 consecutive ticks (i. e. within the same BTL)

•CONTEMPORANEITY: if the time interval between two events is △T<BTL, the computer considers them as simultaneous (contemporaneous)

#### •MEASUREMENT:

- 2 events, whose real time distance is  $\Delta T$ , are considered as within N\*BTL < M( $\Delta T$ ) < (N+1)\*BTL N=floor( $\Delta T$ /BTL)

- events, whose time distance is N\*BTL, can correspond to a real time interval ∆T:

University of Pavia - Francesco Leporati - Industrial Informatics and Embedded Systems 2018

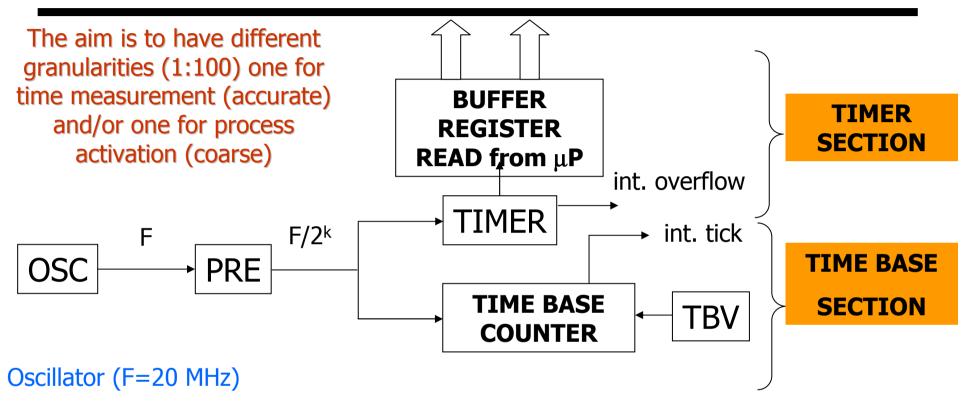

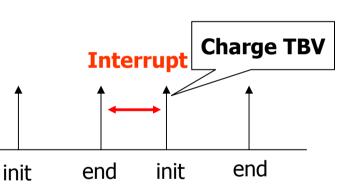

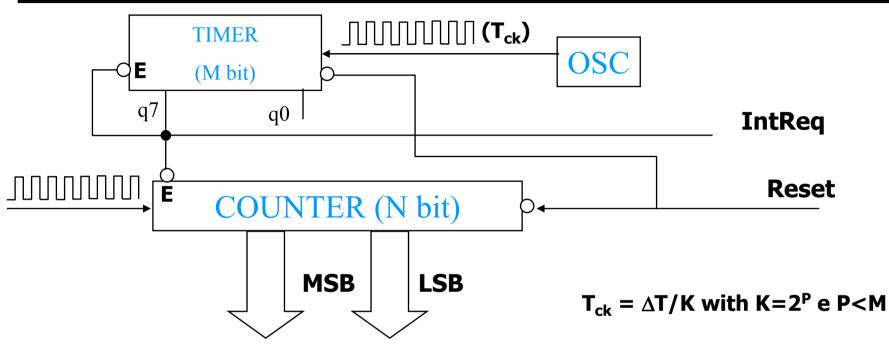

# **TYPICAL TIMING SYSTEMS (TIMERS)**

Prescaler (frequency division,  $2^{k}=1-256$ )

TIMER = N bit binary cyclic counter (16-24)

TIME BASE COUNTER = 1 tick when the set period (TBV) ends + restoration TBV

**Decrement counters**

# **TYPICAL TIMING SYSTEMS (TIMERS)**

#### • TIMER section

TIMER RESOLUTION (count units) =  $2^{k}/F=UTL$

TIMER PERIOD =  $2^{N} * 2^{k}/F$

BTL=  $2^{N}$  (on the overflow)

(COUNT+TBV) mod2<sup>M</sup>=COUNT+TBV-2<sup>M</sup>

$= 2^{M} - x + TBV - 2^{M} = TBV - x$

to include counts lost due

to interrupt latency

- <u>TIME BASE section</u>

- TIME BASE COUNTER RESOLUTION =  $2^{k}/F=UTL$

TIME BASE COUNTER PERIOD = TBV  $* 2^{k}/F$

- •Set TBV automatically or ...

- •Explicit setup within the sw routine that manages tick interrupt but ...

- ●(CONTEGGIO+TBV) mod2<sup>M</sup>

### SOME IDEAS

F=1 MHz, Prescaler=1  $\Rightarrow$  period 1µsec, if N=16  $\Rightarrow$  65000 µsec

F=1 MHz, Prescaler=256  $\Rightarrow$  period 256 $\mu$ sec, if N=16  $\Rightarrow$  16 sec

F=20 MHz, Prescaler=256  $\Rightarrow$  period 12.5 $\mu$ sec, if N=24  $\Rightarrow$  200 sec

| Process activation            | $\Rightarrow$ TIME BASE COUNTER (TBC) |

|-------------------------------|---------------------------------------|

| Time stamping (date and time) | $\Rightarrow$ tick TBC                |

|                               | $\Rightarrow$ overflow TIMER          |

| Interval measurement          | $\Rightarrow$ TIMER                   |

NB. If long intervals are measured we need a sw variable onto which to store the counter values. This implies a partial un alignment between the total sw counter value and the hw register (containing something like a «fractional part» of the overall value).

Pulses are acquired to calculate the velocity (i. e. frequency) of an object Angular velocity or (scale factor) linear velocity can be determined <u>Problem data</u>

- Encoder granularity = (round or meter/pulse)<sup>-1</sup> => quantization effect

- Maximum and minimum frequency to be measured

- Pulse (usually given by a sensor) duration

#### <u>Specs</u>

- Measurement production frequency (acceptable depending on the particular phenomenon to be measured)

- Delay between the acquisition instant and the moment to which it is related

- Errors (relative vs. absolute, related to measurement value or to the full scale value, Erm% vs. Erf%)

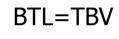

# **VELOCITY CALCULATION**

Pulses are counted during a known time interval

#### What is measured is an "average velocity"

### **Pulse acquisition techniques**

#### Software

Cyclic (Tc period) pulse acquisition If time for reading negligible and Tg granularity of the used clock (BTL\* UTL) Error on the event detection: -Ta<E<Tc

#### Interrupt

The signal carrying the pulse is connected to the interrupt pin of a microprocessor

$T_{lat.max}$  = max. latency of the interrupt service routine

Te = execution time of the interrupt service routine

Error on the event detection: -Tg+Te<E<T<sub>lat.max</sub>+Te

#### Hardware

Dedicated circuits with working times negligible with respect to event duration

Error on the event detection: -Tq<E<0

# Pulse count during time interval: I-SW, T-SW

#### •Sw routine executed with period Tc:

- Input port read

- if positive (raising up) edge I count++;

- if positive edge T vel=(enc. granularity)\*counter\_val/ $\Delta$ T; count=0;

#### Constraints

Tc< minimum pulse duration  $\Rightarrow$  f Tc< 1/2 (f = pulse frequency) f<sub>P</sub> (measure production freq.) = 1/ $\Delta$ T; f<sub>min</sub> (minimum detectable frequency) > 1/ $\Delta$ T

#### •Errors

DTM= real (effective) count interval;  $n_p$ =real n° of pulses DTM f = real signal frequency =  $n_p$  /DTM;  $f_m$  = measured frequency = n (counter value) / $\Delta$ T

Quantization err. on pulse identification [-1 ... 1]  $\Rightarrow$  n<sub>p</sub> -1 < n < n<sub>p</sub> +1 Time err. on  $\Delta T$  estimation [-Tc ... +Tc]  $\Rightarrow \Delta T$  -Tc < DTM <  $\Delta T$  + Tc

f( $\Delta$ T -Tc )-1/  $\Delta$ T < f<sub>m</sub> < f( $\Delta$ T + Tc) +1/  $\Delta$ T

# Pulse count during time interval: I-HW, T-int

•N bit counter connected to a microprocessor port, read during interrupt routine at the beginning and at the end of  $\Delta T$ . Steps of the interrupt service routine:

- interrupt disable and context saving

- count = present counter value previous value;

- freq = count/  $\Delta T$ ;

- previous value = present counter value;

- context restore and interrupt enable

#### •Constraints

$$f_{max} \Delta T < 2^{N} (f=frequency of pulses); f_{P} = 1/\Delta T; f_{min} > 1/\Delta T$$

#### •Errors

Quantization error on pulses identification [-1 ... 1] Time error on  $\Delta T$  estimation [-T<sub>Imax</sub> ... +T<sub>Imax</sub>]

$$f(\Delta T - T_{Imax}) - 1/\Delta T < f_m < f(\Delta T + T_{Imax}) + 1/\Delta T$$

### Pulse count during time interval: I-HW, T-HW

#### Constraints

$f_{max} \Delta T < 2^{N}$  (f= pulse frequency);  $f_{P} = 1/(\Delta T + T_{lmax})$ ;  $f_{min} > 1/\Delta T$

#### •Errors

Quantization error on pulses identification [-1 ... 1] Time error on  $\Delta T$  estimation [-T<sub>ck</sub> ... 0]

$$f(\Delta T - T_{ck}) - 1/\Delta T < f_m < f\Delta T + 1/\Delta T$$

### **Considerations on pulse count during time interval**

- •Typical mode: interrupt for time, pulse count with counter

- for a good resolution  $\Delta T >>$  pulse period

- •Constant quantization error on frequency measurement  $(1/\Delta T)$

- $\bullet\Delta T$  has to be chosen considering the minimum frequency to be measured and the relative error

#### **TRADEOFF ON ERRORS**

- $\bullet \Uparrow \Delta T, \Downarrow$  errors and measurable frequencies  $\Downarrow, \Uparrow$  measureent delay

- $\bullet \Downarrow T_{ck}, \Downarrow \text{ errors, } \Uparrow \text{ timer bits}$

- $\bullet \Downarrow T_{latency \, int.} \Downarrow errors, \Uparrow process management complexity$

- $\Downarrow$  Tc  $\Downarrow$  errors and measurable frequencies  $\Uparrow, \Uparrow$  CPU load

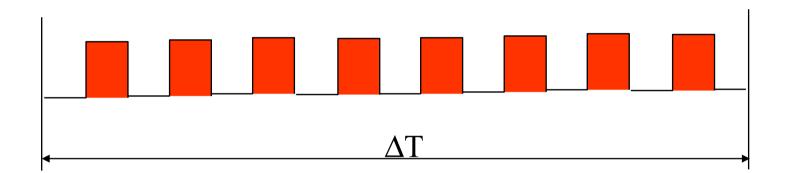

#### Measure of the interval between two consecutive pulses

N bit free-running counter

Time pulses with duration T<sub>ck</sub>

interrupt to acquire the I and the II pulse

interrupt service routine:

context\_saving

temp=read counter;

freq=1/ (temp-prec);

prec = temp;

Context\_restore

#### •Constraints

$T_{ck} 2^N > 1/f_{min}$ ;  $f_P = f$  to measure (minimum  $f_{min}$ );  $f_{max} < 1/T_{ck}$

#### •Errors

Time quantization error  $[-T_{ck} \dots T_{ck}]$ Time error on pulses identification  $[-T_{lmax} \dots + T_{lmax}] \qquad T_{lmax} = max$ . interrupt latency

$$f/1+f(T_{ck}+T_{lmax}) < f_m < f/1-f(T_{ck}+T_{lmax})$$

# Considerations on the measurement of the interval between two pulses

- typical mode: that showed

- null frequency measurement is critical

- variable acquisition period  $(f_p)$  and measurement production

- minimum resolution when frequency is high, max. when it is low

- measur. interval = N pulses, with N set depending on the chosen resolution

- $\Delta T$  chosen on the basis of the minimum frequency

#### **COMPROMESSI SU ERRORI**

$\Downarrow$  T<sub>ck</sub>,  $\Downarrow$  errors,  $\Uparrow$  f<sub>max</sub> detectable,  $\Uparrow$  timer bits

$\Downarrow T_{latency int.} \Downarrow errors, \uparrow f_{max}$  detectable,  $\uparrow complexity$

The frequency of a pulse train must be measured in the variable range of [5 KHz ... 500 KHz]. The measurement must be provided every  $\Delta T$  sec, allowing a small tolerance in the periodicity due to the real availability of the CPU:

- •Describe how the chosen technique works and choose suitable devices so as the uncertainty range affecting the measure in the worst case is [-0.15% ... + 0.1%];

- •Verify that the constraints required by the chosen technique are satisfied;

- determine the maximum and minimum frequencies really measurable with the imposed constraints;

- Calculate the uncertainty range in the frequency measurement if the quantization error on the ∆T interval estimation is supposed to be equal to +/- "quantum".

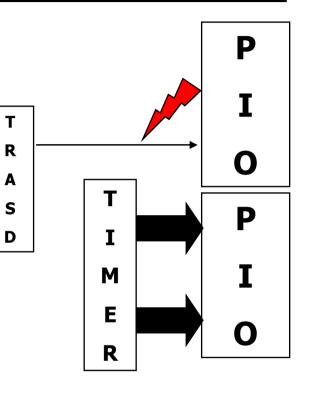

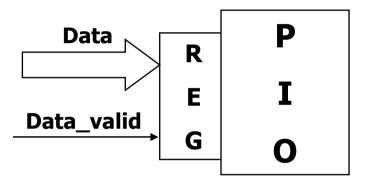

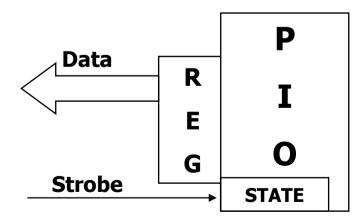

### Pulse acquisition for synchronising

events corresponding to a valid information

• peripheral ready to receive

• Data\_valid; in A, (PORTA\_PIO)

• Strobe from peripheral; out A, (PORTA\_PIO)

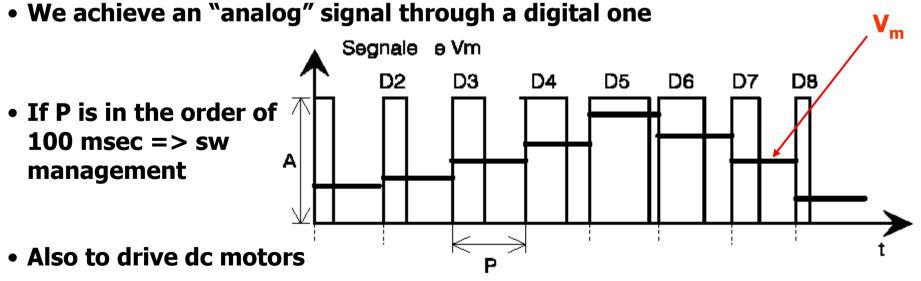

### **PWM PULSE EMISSION**

- Control of processes with a slow behavior that are sensible to the average value of the control signal applied (or of the manipulated variable). For example the environmental temperature

- A pulse with A amplitude and D(t) duration where 0<D(t)<P (period)

- Average value  $(V_m) = A*D/P$  or A\*DC(t) DC = duty cycle (D/P)

- Relative quantization error on  $V_m$  is  $P_{ck}$  (clock granularity) / P

# EXAM TEXT (July 2006)

- Design a system able to heat up an incubator at 20 °C for 2 minutes, using a typical microprocessor equipped with a parallel PIO port connected to a buffer and to a amplification stage with gain A=10

- Suppose that the ratio between environmental temperature and the average applied power (thermal efficiency) is 80 °C/W and that the heater can be electrically modeled as a 1 KΩ resistance.

- Suppose to heat for 10 minutes at 30°, for 5 minutes at 20° and for 5 minutes at 10°: what is the final temperature reached?

- Transformation of electric energy in mechanic (rotation vel. and torque)

- If the voltage supply is fixed a dc motor absorbs a current proportional to the exerted torque (thus it depends on the applied load)

- When the motor is in *stale* it absorbs much more current than in the usual case so to avoid damages is important to define two "limit" magnitudes

- **Stalemate current**: max current absorbed by a motor at the nominal voltage, during the stalemate phase (from hundreds of mA to few A).

- **Stalemate torque**: the torque provided when the driveshaft is blocked (at the startup or due to an external load), with a nominal voltage and maximum current (100 Nm)

69

$$V_{a} = 0 = \text{angular position}$$

$$University of Pavia$$

$$(0) = 0 = \text{angular position}$$

$$(0) = 0 = 0 = 0$$

$$(0) = 0 = 0$$

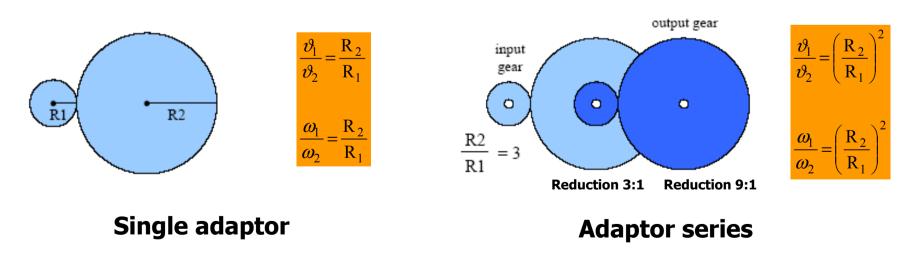

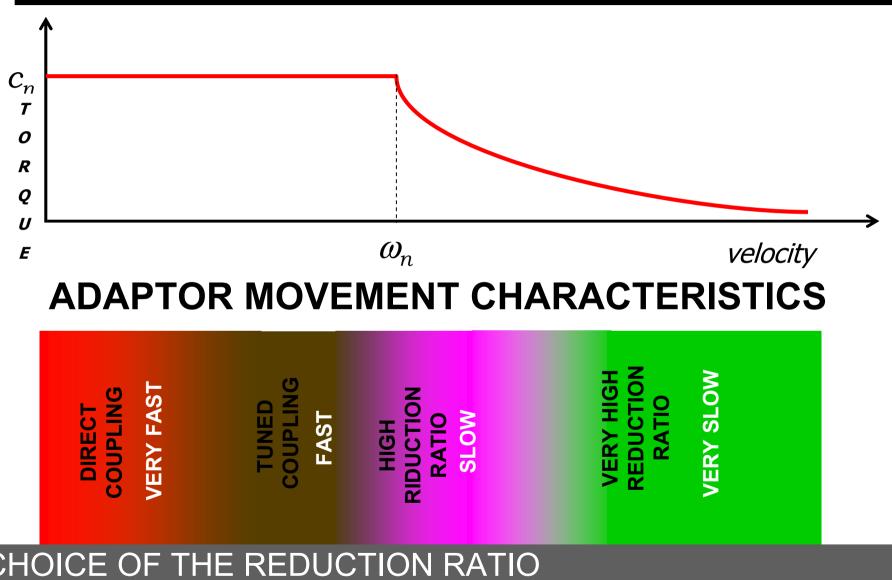

- Sometimes the required velocity is less than that the motor can reach

- Suitable gears can be used (adaptors) that diminish  $\omega$  by a suitable constant factor. The ensemble motor + adaptor can be defined as *motoadaptor*

- The adaptors can be used individually or coupled to regulate the overall angular velocity

Let's consider the mechanical power P conservation,  $\Gamma \omega = \Gamma' \omega'$

Thus when the angular velocity drops down due to the effect of an adaptor the exerted torque correspondingly augments

In other words, if  $\omega = n\omega'$  then  $\Gamma' = n\Gamma$

Finally, since the mechanical behavior of a dc motor can be described by

$\Gamma = \Gamma_0 + \gamma \omega + J \omega$   $\Gamma_0$  effective torque,  $\gamma$  friction and J inertia

$\Gamma' - n\Gamma_0 = (J_R + n^2 J)\omega' + (\gamma_R + n^2 \gamma)\omega'$   $\Gamma'$  new torque,  $\gamma_R$  friction and  $J_R$  inertia of the adaptor

Significant increase of inertia and friction

Instabilities and hysteretical behavior due to mechanical play

The motoadaptors can be effective where high precision is not required

72

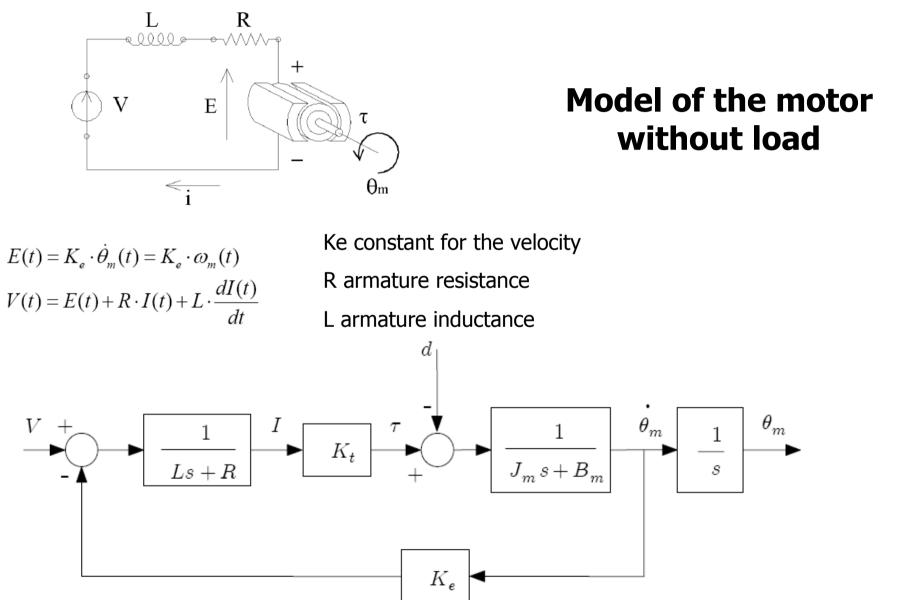

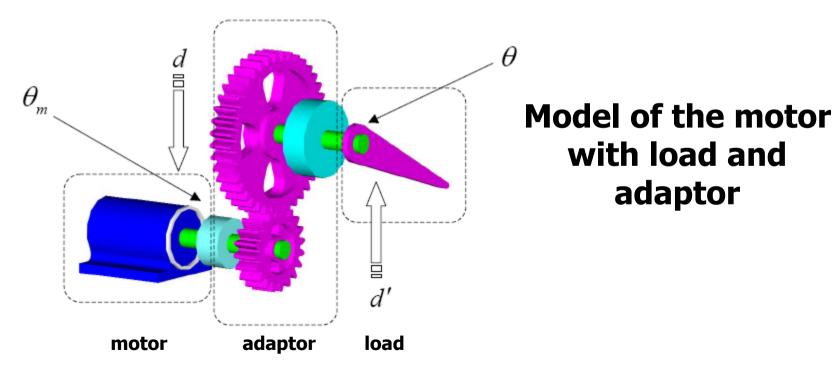

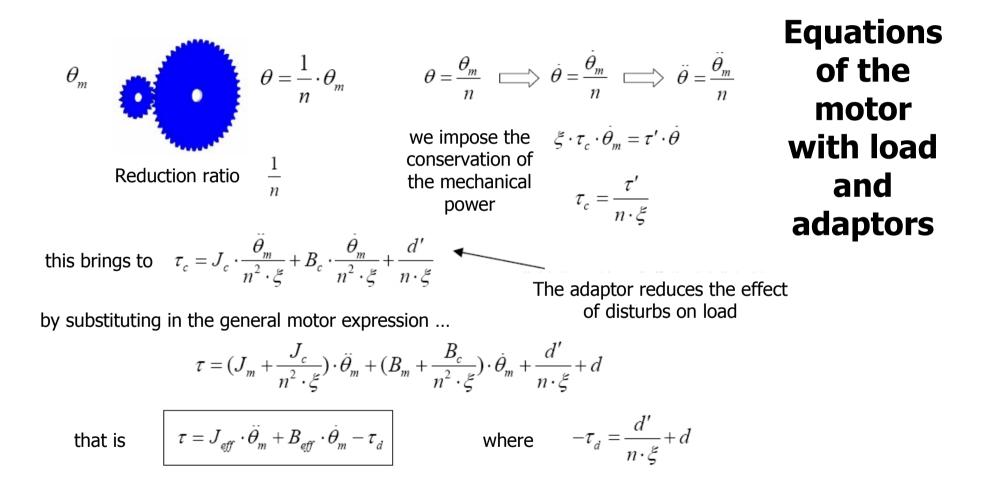

Model of the mechanical part:

$$\tau = J_m \cdot \ddot{\theta}_m + B_m \cdot \dot{\theta}_m + d + \tau_c$$

Similar approach to describe the load components:

$$\tau' = J_c \cdot \ddot{\theta} + B_c \cdot \dot{\theta} + d'$$

*d* = not manipulable inputs, frictions, phenomena without models

$\tau_c$  = effective torque applied to load plus adaptor

$\tau'$  = load torque

University of Pavia - Francesco Leporati - Industrial Informatics and Embedded Systems 2018

University of Pavia - Francesco Leporati – Industrial Informatics and Embedded Systems 2018

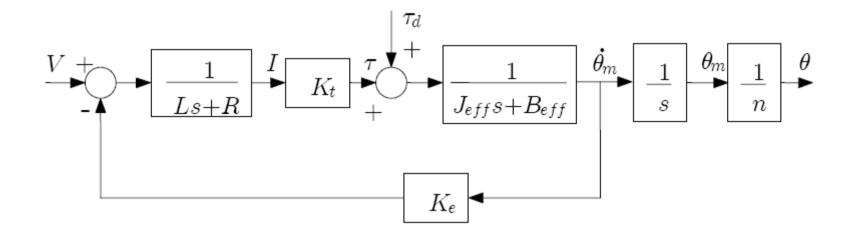

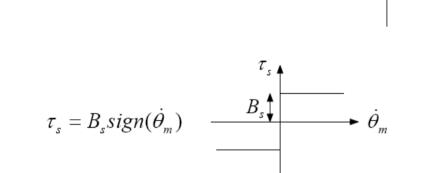

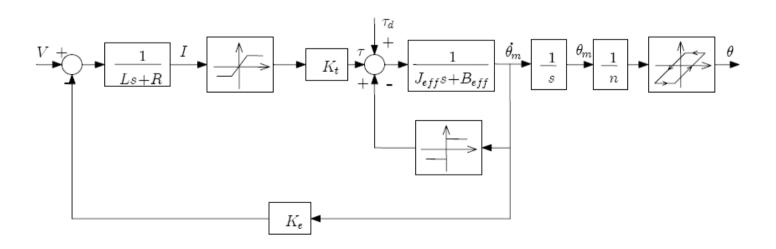

#### Model of the motor with load and adaptor

Saturation

Dry friction

(for example due to current limitation)

#### Possible non linearities

Adaptor hysteresis (due to possible mechanical plays)

76

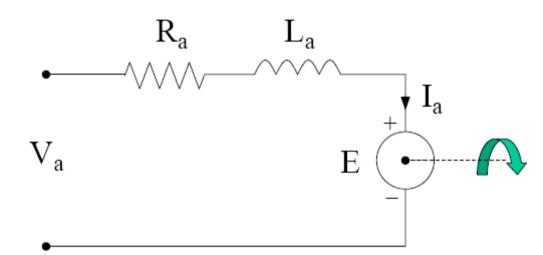

- DC motor, simplified equivalent electric circuit:

- • $V_a$  = supply voltage

- • $I_a$  = supply current

- •E = back electromotive force

- • $R_a$  = armature resistance

- • $L_a$  = armature inductance

#### Model:

- $\bullet V_a = E + R_a I_a$

- •E = k<sub>e</sub>ω

- $\bullet P_a = V_a I_a = EI_a + R_a I_a^2$

E back emf

$k_{\rm e}$  constant for the velocity

absorbed electric power = mechanical power + power lost in the armature

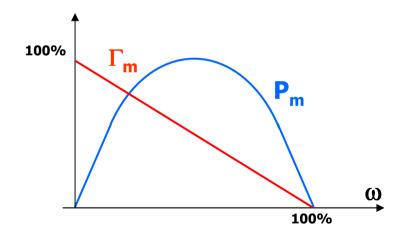

#### •DC motor, characteristic:

$$P_m$$

= mechanical power = E  $I_a = \Gamma_m \omega$

$$\Gamma_{\rm m}$$

= motor torque =  $k_{\rm t}I_{\rm a}$

#### •considering that:

$$I_a = (V_a - E)/R_a$$

and  $E = k_e \omega$  we obtain that  $\Gamma_m = k_t (V_a - k_e \omega)/R_a$

The torque diminishes when the angular velocity increases

At the beginning the mechanical power grows up with the angular velocity then diminishes with a typical "bell" behavior

#### **TORQUE-VELOCITY REAL STATIC CHARACTERISTIC**

University of Pavia - Francesco Leporati – Industrial Informatics and Embedded Systems 2018

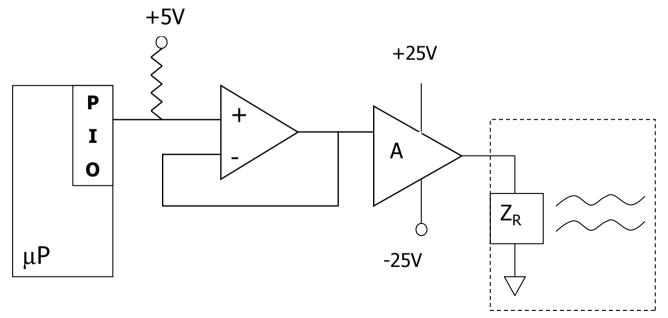

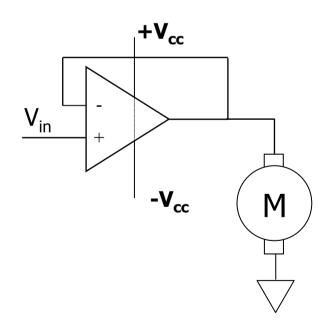

#### •DC motors, power supply:

Motors absorb a lot of current (0.5 : 1) A so requiring specific driving circuits (power drivers)

Two possible kinds of driving: linear and on-off

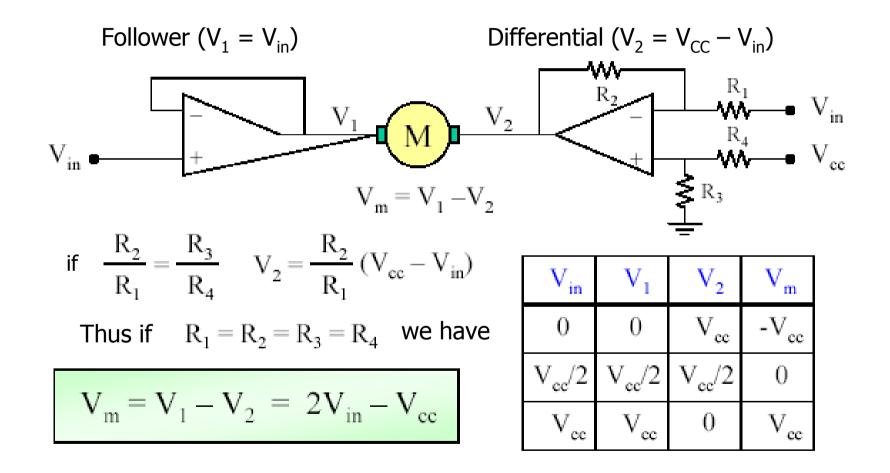

To manage a bi-directional rotation a bipolar power supply  $V_{in}$  +/- is required

If the resistant torque (the ensemble that opposes to rotation inertia, frictions, disturbs, ...) is negligible a good linearity can be obtained between  $V_{in} \in \omega$

Should not a bipolar supply available, a "bridge" solution can be introduced

•DC motors, linear driving (a bipolar voltage using a unipolar one):

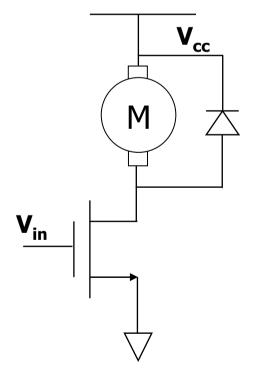

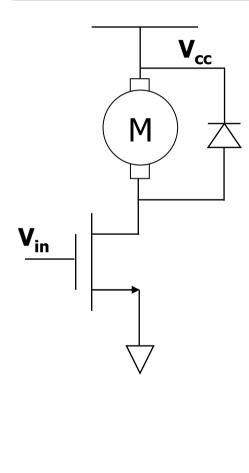

#### •DC motor, on off driving:

If the linear driving dissipates too much power, it can be used only in case of motors that absorb few Watts

To reduce the dissipated power MOS switching devices in on (saturation)/off stage

Dissipated power =  $V_{ce}$  I

If MOS off, I=0 no dissipated power

If MOS in saturation,  $V_{ce} \cong 0$  so dissipated power  $\cong 0$

"Outflow" diodes for the current are required to avoid excessive voltages at the MOS drain (although it is fast and able to carry high currents)

Limit: the motor will run at the maximum velocity (only mono-direction) otherwise it will be stopped

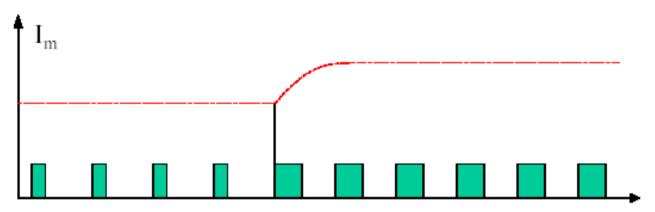

#### •CC motor, on off driving:

For this reason it is useful to drive the motor through duty cycle variable pulses (PWM) so as to obtain a enough pulse frequency with an average supply voltage proportional to the pulses duty cycle.

However it is still not possible a bi-directional rotation

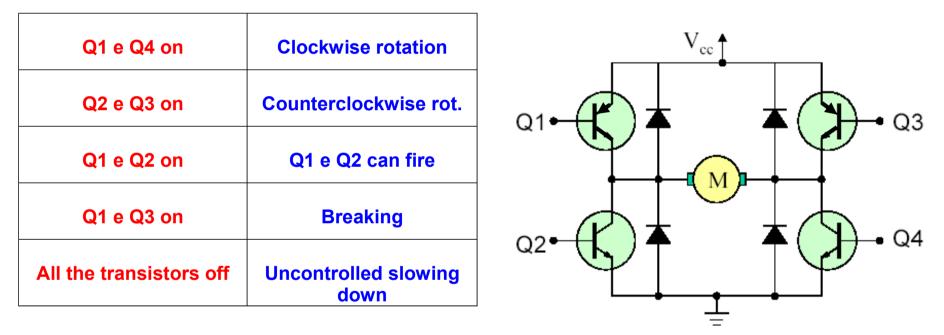

#### •DC motor, H bridge driving (for small laboratory robots):

the "H-bridge" circuit allows to control the sense of rotation.

If two transistors on the same side are active (shoot-through) a big current passes between Vcc and ground. However, now the load is no more the motor (who absorbs the most of the current and so the voltage drop) as before thus the bridge could be damaged.

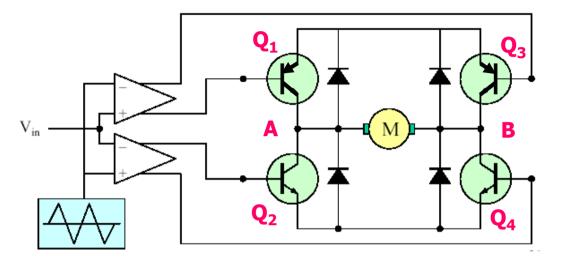

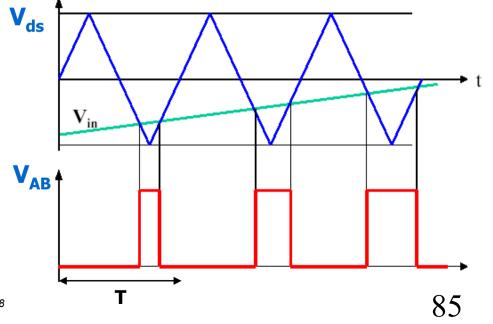

#### •CC motor, H bridge driving:

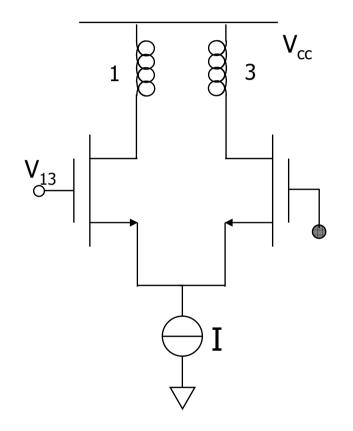

If we do not want to make the microprocessor serving as pulse emitter, a suitable electronic net could be used to activate transistors

$V_{in} > V_{ds} Q_3 e Q_2$  active

$V_{in} < V_{ds} Q_1 e Q_4$  active

Within a period T of the input signal  $V_{ds}$  the motor rotates for a certain time in a direction and for the remaining in the opposite direction; for the long-term time the resulting direction will be proportional to the sum of the different rotations in the different intervals: if  $V_{in}$  would be horizontal and exactly located in the medium of  $V_{ds}$ , the motor would be stopped (**Locked anti-phase PWM**)

University of Pavia - Francesco Leporati - Industrial Informatics and Embedded Systems 2018

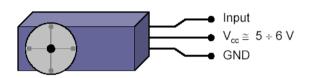

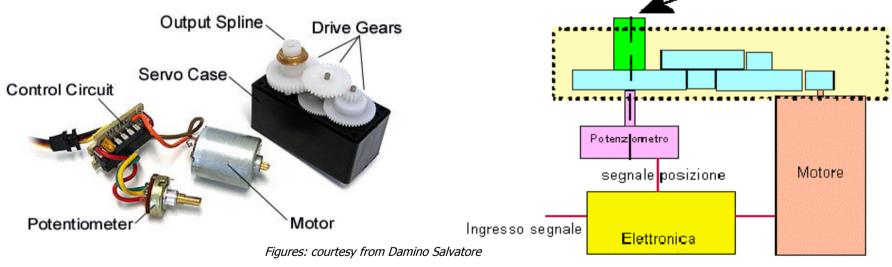

# **PWM PULSE EMISSION: SERVO MOTORS**

They encapsulate dc motor, adaptors, control electronic e position control through a potentiometer for detecting the shaft position and rotation limit switch (to protect the movement area)

.sse uscita

Characteristics: torque, rotation velocity, maximum rotation angle. Used in robotics applications

Orders of magnitude:

Rotation angle:  $\pm 90^{\circ}$ , torque: 3-20 Kg\*cm (but even 20 Nm), absorbed current: 1-10 mA on rest and  $\sim 1$  A full load, rotation velocity: up to 9000 rpm, weight:  $\sim 150$  gr.

University of Pavia - Francesco Leporati – Industrial Informatics and Embedded Systems 2018

## **PWM PULSE EMISSION: SERVOMOTORS**

#### •Servomotors:

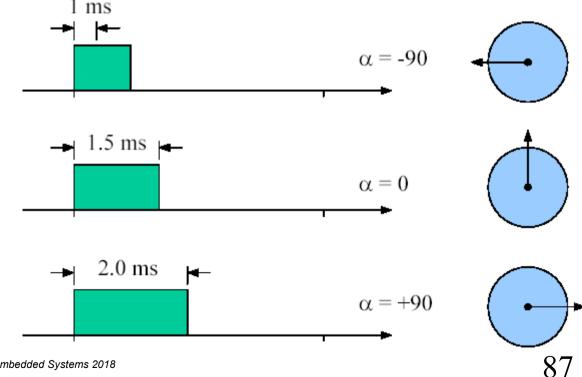

Again PWM pulses are used, and the duty cycle determines the shaft position with respect the previous one (the incremental amount of the rotation): for example, depending on the motor type, a certain pulse duration corresponds to  $-90^{\circ}$  rotation, if the duration is twice the rotation is  $+90^{\circ}$ , if it is half the rotation is  $0^{\circ}$ . If the servo does not frequently receive pulses it is abandoned without any control.

Usually the repetition period is 20-30 msec, whilst the pulse duration ranges from a 1 msec minimum up to 2 msec max.

The servo is stopped when a "central" pulse duration is provided or due to its natural lost of energy (frictions ...)

Open loop position control

## **PWM PULSE EMISSION: SERVOMOTORS**

#### •Servomotors:

The "response" of the servo depends mainly on the pulse duration more than on the duty cycle since these motors are designed to properly work into a enough wide PWM frequency range within which the behavior is quite similar (not a orthodox PWM).

If for example a servo receives pulses with variable period among 0-70 msec, it may happen that with values close to ~10 msec the servo becomes a little unstable (vibrations), while when the period is > 40 msec, the torque diminishes. Thus a period close to 20 msec could be the right choice (moreover is easy  $\Rightarrow$  50 Hz).

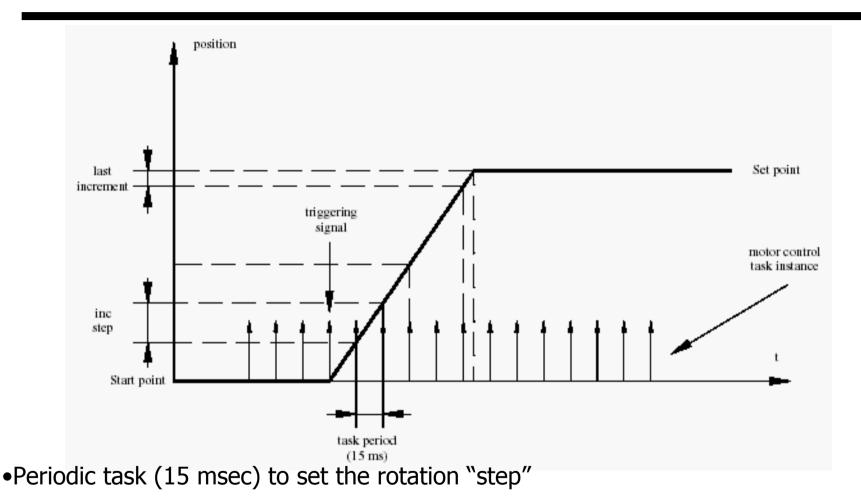

The servo are characterized by a suitable "working curve" to achieve a predetermined motion dynamic.

The "curve" could consist on variable width steps (larger at the beginning, smaller when close to the target) up to reach the set point. It could be useful to control the movement velocity although this is quite difficult since practically the system moves always at maximum velocity.

How to generate the pulse?: a hybrid solution could envisage a  $\mu$ P triggering a timer so as it exits pulses with a duty cycle set again through the  $\mu$ P. It is not possible to completely devote a  $\mu$ P to pulse emission because the required times (sometimes < msec) ask for high frequency routines, with possible  $\mu$ P overload and inaccuracies.

- •At the beginning the step is wide, when the position is close to the target it diminishes

- •The position of the rotating shaft can be evaluated time by time

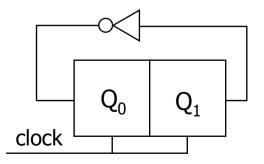

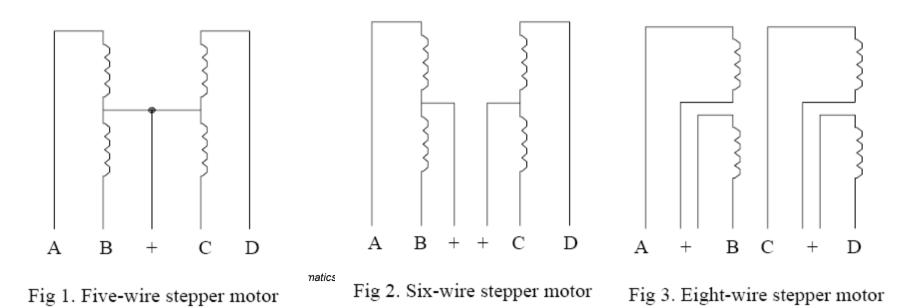

•Step motors: every received pulse correspond to a precise rotation step

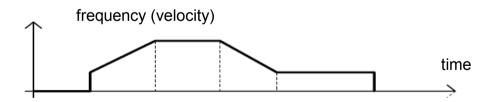

•Low torque, good precision, low cost. Applications: computing systems peripherals, robotics, small applied loads

• Specs:

•Pulse duration enough to drive electronics

•Start frequency (minimum sequence necessary to start rotation) and stop (minimum frequency below which the motor is stopped)

Acceleration and deceleration ramp

•Possible jitters that imply steps lost or vibrations

•Dedicated hw or processors (for example PIC: programmable interface controller, Microchip Risc microcontrollor, low costs)

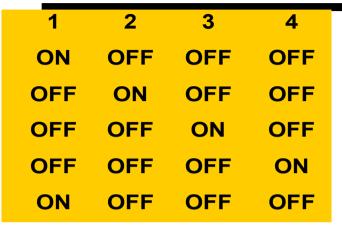

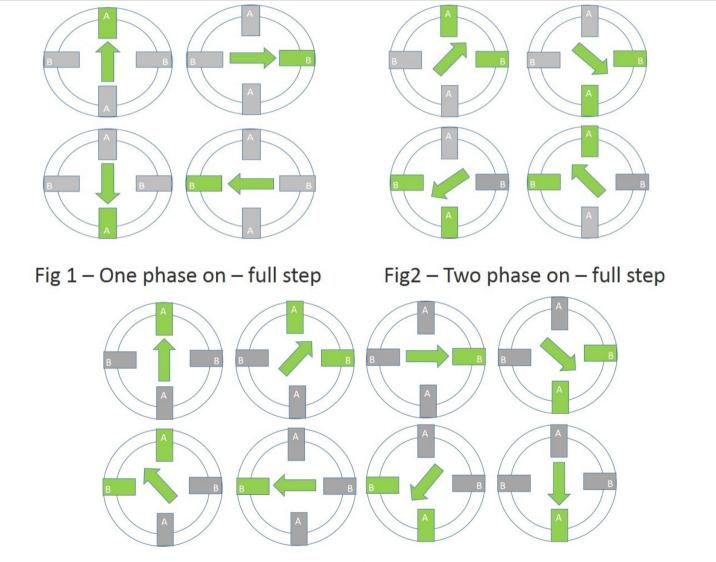

#### Two-phase sequence,

Most commonly used movement (good torque, not negligible power consumption and heat dissipation)

| 1   | 2   | 3   | 4   | <b>V</b> <sub>13</sub> | <b>V</b> <sub>24</sub> |

|-----|-----|-----|-----|------------------------|------------------------|

| ON  | ON  | OFF | OFF | +                      | +                      |

| OFF | ON  | ON  | OFF | -                      | +                      |

| OFF | OFF | ON  | ON  | -                      | -                      |

| ON  | OFF | OFF | ON  | +                      | -                      |

| ON  | ON  | OFF | OFF | +                      | +                      |

How to provide clock?

*Wave*: less torque with respect two phase (1vs1.4)

*Half step*: the step number is twice (precision) but the torque is irregular and the power consumption not constant

| 1   | 2   | 3   | 4   |

|-----|-----|-----|-----|

| ON  | OFF | OFF | ON  |

| ON  | OFF | OFF | OFF |

| ON  | ON  | OFF | OFF |

| OFF | ON  | OFF | OFF |

| OFF | ON  | ON  | OFF |

| OFF | OFF | ON  | OFF |

|     |     |     |     |

92

Fig3 - One-two phase on - half step

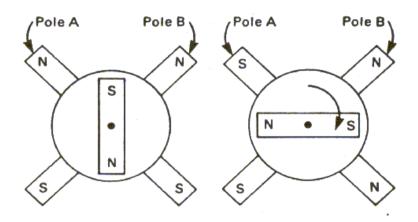

| 1a. WAVE DRIVE MODE |                  | 1b. NORMAL DRIVE MODE |                  | 1c. HALF STEP MODE |                         |                   |                       |

|---------------------|------------------|-----------------------|------------------|--------------------|-------------------------|-------------------|-----------------------|

| Transistor Accesi   | Posizione Rotore | Transistor Accesi     | Posizione Rotore | Transistor Accesi  | <b>Posizione Rotore</b> | Transistor Accesi | Posizione Rotore      |

| Q1                  | S<br>S           | Q1 e Q2               | S N S N          | Q1                 | s N S                   | Q3                | S<br>S<br>N           |

| Q2                  | s(N s)N→         | Q2 e Q3               | S N N N          | Q1 e Q2            | S N S N                 | Q3 e Q4           | N S N S               |

| Q3                  | s<br>s<br>N      | Q3 e Q4               | N S N            | Q2                 | s(N S)N→                | Q4                | N(S N) S ←            |

| Q4                  | N(S N) S 🔶       | Q4 e Q1               | N<br>N<br>S<br>S | Q2 e Q3            | S N N                   | Q4 e Q1           | N<br>N<br>S<br>N<br>S |

University of Pavia - Francesco Leporati – Industrial Informatics and Embedded Systems 2018

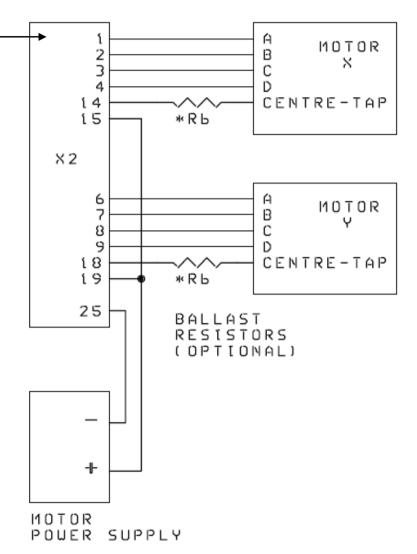

Interface µP 25 pin

| X2 pin         | Motor               | Coil       |  |

|----------------|---------------------|------------|--|

| 1              | Х                   | А          |  |

| 2              | Х                   | В          |  |

| 3              | Х                   | С          |  |

| 4              | Х                   | D          |  |

| 14, 15, 16, 17 | Х                   | CENTER-TAP |  |

| 6              | Y                   | А          |  |

| 7              | Y                   | В          |  |

| 8              | Υ                   | С          |  |

| 9              | Y                   | D          |  |

| 18, 19, 20, 21 | Υ                   | CENTER-TAP |  |

| 10, 11, 12, 13 | INPUTS              |            |  |

| 5              | NOT CONNECTED       |            |  |

| 22, 23, 24, 25 | POWER SUPPLY GROUND |            |  |

| HSTEP motorSet motor to use half-step drive sequence.                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2PHASE motorSet motor to use two-phase drive sequence. This is the default drive sequence.                                                                |

| WAVE motorSet motor to wave drive sequence                                                                                                                |

| RATE motor val1 <val2>Set the delay rate between steps (in milliseconds). Range from 1 to 50,000.</val2>                                                  |

| DIR motor $\langle CW, CCW \rangle$ Set the direction of rotation. CW = clockwise, CCW = counter-clockwise. If no direction is given then it is reversed. |

| STEP motor val1 <val2>Step motor by val1 steps. If motor is both then val1 refers to `X" and val2 refers to `Y'.</val2>                                   |

| WAIT motorWait for the previous motor command to finish before executing the next command for that motor.                                                 |

| SPIN motorContinuously step motor. Not affected by 'WAIT'.                                                                                                |

| STOP <motor>Immediately stop the current command for motor. If no motor is specified then stops both.<br/>Ignores `WAIT'.</motor>                         |

| MANUALManually step motors. Another menu appears.                                                                                                         |

| LOOPTIL input(n) HIGH,LOW where n=1, 2, 3 or 4.Wait for the specified input to go high or low before continuing.                                          |

| DELAY millisecondsWaits the specified delay time before continuing. Range = 1 to 50,000.                                                                  |

| ECHO ON or OFFIf ON (default) then all commands are echoed to the output.                                                                                 |

| PRINT messageto output                                                                                                                                    |

| VERPrint version number                                                                                                                                   |

| ENDWait for all motor commands to finish then quit                                                                                                        |

| QUITQuit program immediately                                                                                                                              |

| HELPDisplay above summary                                                                                                                                 |

|                                                                                                                                                           |

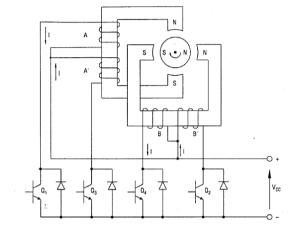

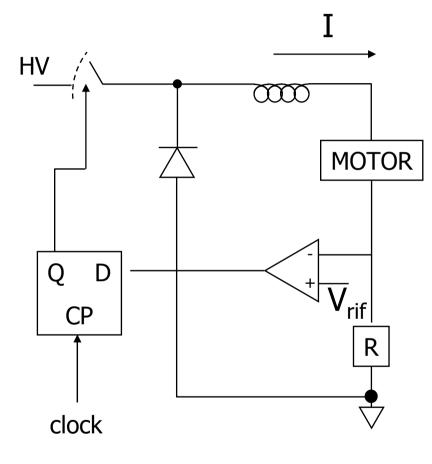

### **STEPPER MOTORS: PWM POWER SUPPLY**

The motor receives a constant current, obtained through a HV voltage necessary to provide fast commutations (time constant L/r)

If current is  $< V_{rif}/R$  the flip flop close the switch so supplying the motor with a 100 V voltage. Alternatively (open switch), the circuit is grounded through a diode.

The flip flop closes the switch depending on a clock period that allows to regulate the opening and closing intervals (that means the duty cycle).

The inductor serves as "regulation maker" allowing a smooth passage among the levels of the current (high low high low) without shocking the motor.

ON OFF control.

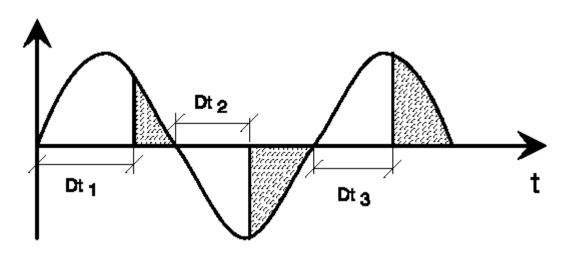

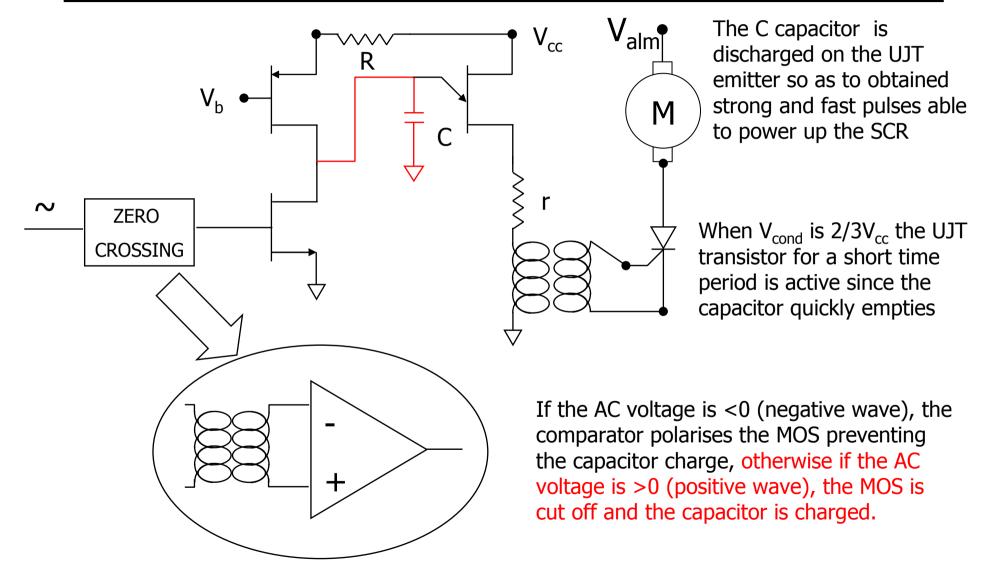

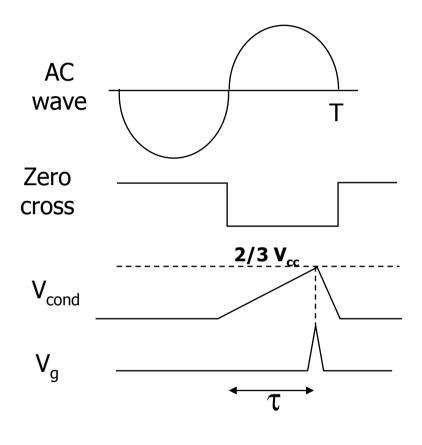

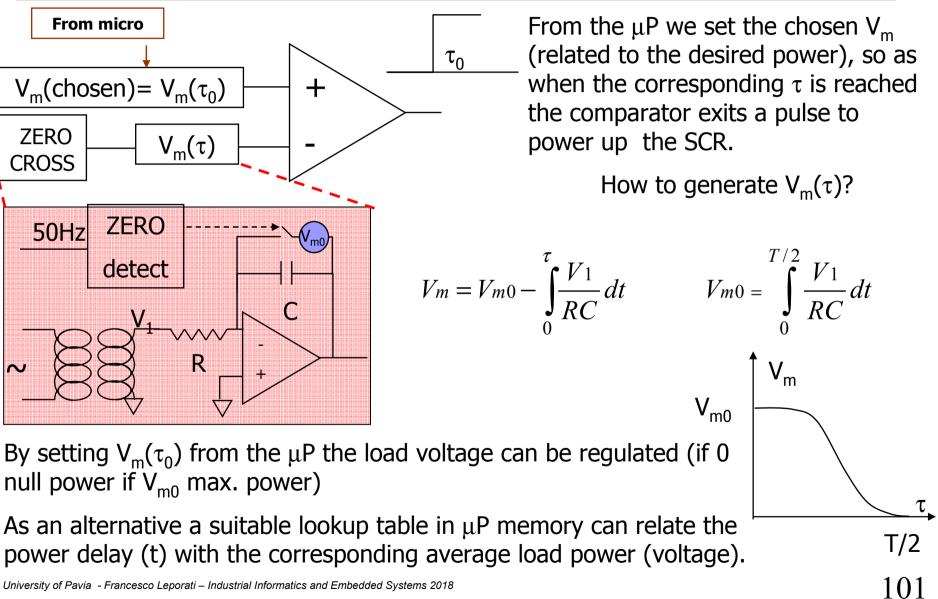

- "controlled" AC power supply through SCR/TRIAC

- The wave passage through zero must be revealed then a  $\mu\text{P}$  should provide the pulses for SCR/TRIAC activation

- Wave period 20 msec, the passage through zero has to be detected with very high precision  $\Rightarrow$  HW solution

- $\bullet$  D(t) can be settled through a sw routine or through a timer with a interrupt to  $\mu P$

- Non linear relationships between the average power provided and the power up delay

University of Pavia - Francesco Leporati – Industrial Informatics and Embedded Systems 2018

$$\tau = \frac{\frac{2}{3}C \cdot V_{cc}}{I_c} \qquad I_c = \frac{V_{cc} - V_b}{R}$$

$$\tau = \frac{2}{3}\frac{RC \cdot V_{cc}}{V_{cc} - V_b}$$

$V_b$  allows to regulate the capacitor charge velocity so to establish when ( $\tau$ ) to power up the SCR (i. e. the provided power).

High non linearity between the delay and the power applied to the load.

University of Pavia - Francesco Leporati – Industrial Informatics and Embedded Systems 2018

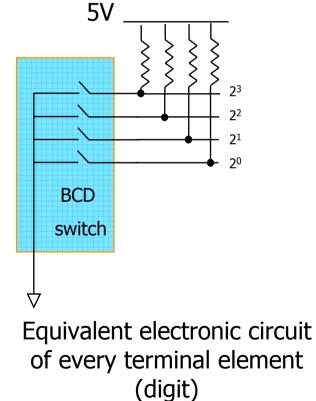

# HW CODED (SETUP) VALUES: BCD SWITCHES

Signals alone do not bring significant information: it's their ordered ensemble that represents an information

A typical example is the acquisition of BCD numeric values for the digital set point of a regulation chain = contraves 5V

Multiswitch contrave with rotational setup of the digits Multiswitch contrave with linear (push button) setup of the digits

# HW CODED (SETUP) VALUES: BCD SWITCHES

Possible problems during commutations:

- •Brushing, slithering and contacts rebounds

- •Irregular commutations due to long usage

- •Passage through halfway not significant values

- •Casual order through which the operator moves digits

- •Several input instructions (if for example more than 4 BCD digits and  $\mu$ P with <= 16 bits)

Solutions:

- •Ok temporarily "out of range" values

- •A suitable "settlement time" (SW) after which values are accepted

- •Validation button (HW)

- •A sw conversion from the BCD value to the machine binary representation is needed ...

## **CODED VALUES: ABSOLUTE ENCODERS**

Gray code is used to minimise the error due to a bad alignment of the optics internal to the encoder.

#### Pseudocode algorithm

```

commutare := 0

i := N-1

while i >= 0

BitBin[i] := BitGray[i]

if commutare = 1

then BitBin[i] := not BitBin[i]

commutare := BitBin[i]

i := i-1

endwhile

```

#### **C** version

```

int Gray12_bin (NumGray);

{

int commuta,i,mask;

valore = NumGray;

i = 12;

mask = 0x800;

commuta = 0;

while (i > 0)

{

valore ^= commuta;

commuta = valore & mask;

commuta >>= 1;

mask >>= 1;

i--;

}

return (valore);

}

```

#### **ASSEMBLY VERSION**

Routine that takes as input the variable VALORE in Gray code 12 bit and exits with the pure binary converted value in AX (accumulator) register.

| ,           |                                               | Integer | Gray code | Binary code |

|-------------|-----------------------------------------------|---------|-----------|-------------|

| GRAY12_BIN: |                                               | 0       | 0000      | 0000        |

| MOV         | CX,12                                         | 1       | 0001      | 0001        |

| MOV         | AX,800H                                       | 2       | 0011      | 0010        |

| SUB         | BX,BX                                         | 3       | 0010      | 0011        |

| CICLO:      | ,                                             | 4       | 0110      | 0100        |

| XOR         | [VALORE],BX                                   | 5       | 0111      | 0101        |

| MOV         | BX,[VALORE]                                   | 6       | 0101      | 0110        |

| AND         |                                               | 7       | 0100      | 0111        |

|             | BX,AX<br>AX,1<br>BX,1<br>CICLO<br>AX,[VALORE] | 8       | 1100      | 1000        |

| SHR         |                                               | 9       | 1101      | 1001        |

| SHR         |                                               | 10      | 1111      | 1010        |

| LOOP        |                                               | 11      | 1110      | 1011        |

| MOV         |                                               | 12      | 1010      | 1100        |

| RET         |                                               | 13      | 1011      | 1101        |

|             |                                               | 14      | 1001      | 1110        |

|             |                                               | 15      | 1000      | 1111        |

- A 32 bit microprocessor with working frequency of 50 MHz must measure a pulse train frequency in the range [1Hz-1KHz] with +/- 1% precision.

- The processor must also supply the power to a resistive load with a precision equal to 0.4% and must acquire two BCD numeric values.

- No latency must be taken into account for interrupt tasks scheduling.

- The more accurate technique must be established that allows a reasonable measurement production frequency of the pulses considering the available number of bits.

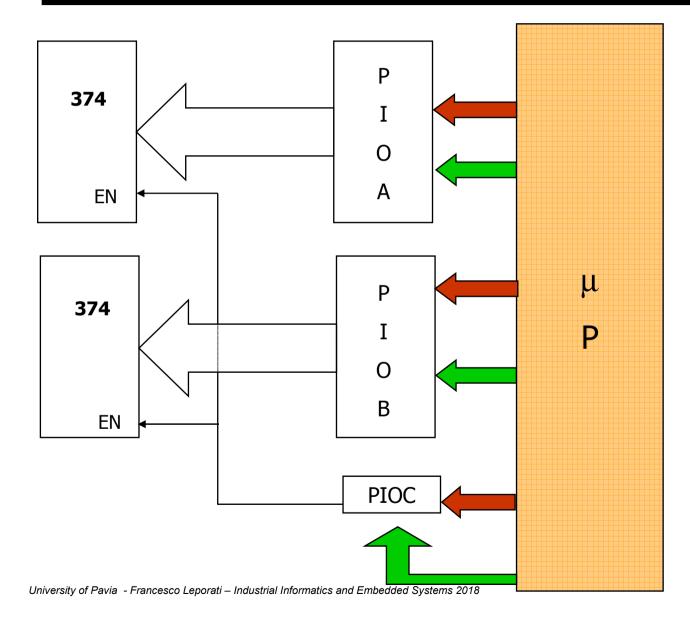

# **OUTPUT CODED VALUES**

We suppose that we have to output more bits than those manageable with a single OUT instruction

OUT (PIOA), reg OUT (PIOB), reg1 OUT (PIOC), WR\_CMD

#### DATA BUS ADDRESS BUS