## Prova d'esame di RETI LOGICHE (Prof. E. Torti)

## Lauree in Ing. Elettronica e Informatica DM 270 26 marzo 2021

CANDIDATO: n. matricola:

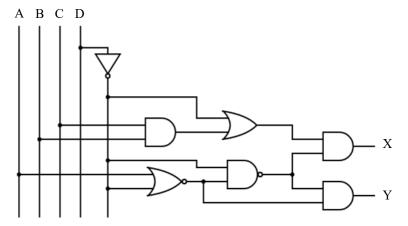

1) Si determini il ritardo di propagazione di entrambe le uscite del seguente circuito logico (considerando anche il ritardo prodotto dalle NOT sugli ingressi), conoscendo le caratteristiche delle porte logiche indicate in tabella (t<sub>PHL</sub> è il ritardo di propagazione per la transizione alto-basso, mentre t<sub>PLH</sub> è il ritardo di propagazione per la transizione basso-alto). Ricavare poi, per entrambe le uscite, le espressioni logiche e semplificarle indicando chiaramente i teoremi/identità/proprietà utilizzati.

| Porta | $t_{\mathrm{PHL}}$ | $t_{PLH}$ |

|-------|--------------------|-----------|

| AND   | 0,1 ns             | 0,4 ns    |

| OR    | 0,3 ns             | 0,1 ns    |

| NOT   | 0,1 ns             | 0,1 ns    |

| NOR   | 0,7 ns             | 0,6 ns    |

| NAND  | 0,3 ns             | 0,6 ns    |

- 2) Si progetti un full-adder, ricavando la tabella di verità, le mappe di Karnaugh e le espressioni algebriche. Utilizzare poi il full-adder come blocco elementare per progettare un sommatore a 5 bit con riporto. Applicare poi la tecnica della contrazione per progettare un circuito "incrementa di 14" per numeri a 5 bit senza riporto in uscita.

- 3) Si spieghino i possibili utilizzi di una look-up table (LUT). Descrivere la struttura di una generica LUT a 2 ingressi. Si progetti poi una LUT a 4 ingressi utilizzando solamente LUT a 2 ingressi e multiplexer 2-1. Con la LUT progettata realizzare poi la funzione:

$$F = AB + B\bar{C} + \bar{A}D$$

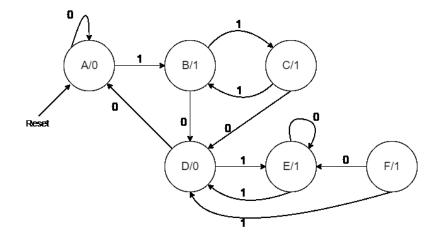

4) Si consideri il seguente diagramma di stato. Eliminare eventuali stati equivalenti, ricavare la tabella di stato ed assegnare agli stati un codice binario secondo la codifica Gray. Implementare poi il circuito utilizzando solo flip-flop di tipo D (non è necessario disegnare tutto il circuito, basta indicare le equazioni e come viene collegato il segnare di reset ai flip-flop). Calcolare poi il costo degli ingressi assumendo che il costo di un singolo flip-flop sia pari a 14 ed ignorando il costo delle porte NOT sugli ingressi. Si indichi poi come sia possibile sostituire i flip-flop di tipo D con flip-flop JK senza apportare modifiche alle rete combinatoria che genera gli ingressi ai flip-flop.

- 5) Si progetti poi un contatore binario sincrono modulo 12 con segnale di ENABLE attivo basso, utilizzando solo flip-flop JK. Considerare gli stati non utilizzati come condizioni di non specificazione. Si indichi poi il costo degli ingressi, assumendo che ogni flip-flop abbia un costo pari a 14.

- 6) Descrivere funzionamento e struttura di un registro a scorrimento bidirezionale con possibilità di caricamento dati parallelo.

- 7) Si consideri il seguente codice VHDL che descrive un contatore a 5 bit. Commentare sinteticamente gli statement del codice (riportare sul foglio il numero della riga seguito dal relativo commento). Spiegare poi come andrebbe modificato il codice per avere un contatore modulo 19. Come andrebbe modificato il codice per includere una porta di SET asincrona che abbia priorità sulla porta RESET. Come andrebbe modificato il codice affinché il contatore commuti sui fronti di discesa del clock?

```

1: library ieee;

2: use ieee.std logic 1164.all;

3: use ieee.numeric std.all;

4: entity cnt5 is

5:

port(

6:

clk, reset, en: in std logic;

7:

Q: out std logic vector(4 downto 0);

8:

co: out std logic

9:

10: end cnt5;

11: architecture arch of cnt5 is

signal count : unsigned(4 downto 0);

12:

13:

begin

14:

process(clk,reset)

15:

begin

16:

if(reset='1') then

17:

count <= "00000":

18:

elsif(rising edge(clk) and (en='1')) then

19:

count <= count + "00001";

20:

end if:

21:

end process;

22:

Q <= std logic vector(count(4 downto 0));

23:

co <= '1' when std logic vector(count(4 downto 0))="11111" and en='1' else

24:

25: end arch;

```