## Prova d'esame di RETI LOGICHE (Prof. E. Torti)

## Lauree in Ing. Elettronica e Informatica DM 270 24 gennaio 2025

## CANDIDATO: n. matricola:

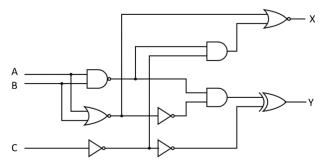

1) Si consideri il circuito in figura sottostante. Si calcoli il ritardo di propagazione del circuito, utilizzando i dati riportati in tabella dove t<sub>PHL</sub> indica il ritardo di propagazione da valore logico alto a valore logico basso e t<sub>PLH</sub> indica il ritardo di propagazione da valore logico basso a valore logico alto. Si indichi infine quale delle operazioni elementari viene svolta dal circuito.

| Porta logica | $t_{ m PHL}$ | $t_{\rm PLH}$ |

|--------------|--------------|---------------|

| AND          | 1,1 ns       | 1,2 ns        |

| NAND         | 0,9 ns       | 0,8 ns        |

| NOR          | 0,6 ns       | 0,7 ns        |

| XOR          | 1,3 ns       | 0,4 ns        |

| NOT          | 0,1 ns       | 0,1 ns        |

- 2) Si considerino due numeri interi con segno A e B, rappresentati in complemento a 2. Il numero A assume valori nel range [-1, 6] mentre il numero B nel range [-6, 7]. Si progetti un circuito logico a costo minimo in grado di realizzare l'operazione 2A+B (rappresentando tutti i risultati possibili), su un numero minimo di bit. Si progetti poi un circuito a costo minimo assumendo che il valore B sia fisso a -1.

- 3) Si descriva la generica struttura di un dispositivo FPGA, approfondendo in particolare i diversi tipi di interconnessione e il loro impatto sulle prestazioni finali del circuito implementato.

- 4) Si progetti un circuito sequenziale dotato di due ingressi A e B e di un'uscita Y. Ad ogni istante n il circuito dovrà produrre l'uscita Y rispettando la seguente specifica:

$$Y_n = (A_n + A_{n-1})A_{n-2}$$

se  $B_n = 0$

$Y_n = A_n A_{n-1} + A_{n-2}$  se  $B_n = 1$

Il circuito dovrà essere a costo minimo e prevedere un segnale di reset (si disegni solo il dettaglio di come viene collegato il segnale di reset, non tutto il circuito). Calcolare il costo degli ingressi assumendo che ogni flip-flop abbia un costo pari a 14.

- 5) Si progetti un contatore in grado di seguire ciclicamente la sequenza di conteggio -3, -1, 3, 0, 2, 1 con un numero minimo di bit. Si progetti il circuito utilizzando unicamente flip-flop di tipo JK considerando le combinazioni non utilizzate in fase di progetto come combinazioni di non specificazione. Si indichi come andrebbe collegato il segnale di reset (si disegni solo il dettaglio di come viene collegato il segnale di reset, non tutto il circuito). Calcolare il costo degli ingressi assumendo che ogni flip-flop abbia un costo pari a 14. Si disegni il diagramma di stato e si indichi come evolverebbe il circuito qualora si presentassero combinazioni considerate come condizioni di non specificazione.

- 6) Si descriva il funzionamento di un buffer a tre stati, discutendo in particolare la sua utilità applicativa nella realizzazione di circuiti logici e dispositivi di I/O, riportando un esempio per ciascuno di questi due casi.

7) Si consideri il seguente codice VHDL che descrive un contatore a 5 bit. Commentare sinteticamente gli statement del codice (riportare sul foglio il numero della riga seguito dal relativo commento). Spiegare poi come dovrebbe essere modificato il codice per includere una porta di uscita che indichi il raggiungimento della massima dinamica di conteggio. Descrivere poi come andrebbe modificato il codice per includere un segnale di set sincrono che imposti la parola si uscita al valore 11111. Descrivere poi come andrebbe modificato il codice per realizzare un contatore modulo 28.

```

1: library ieee;

2: use ieee.std logic 1164.all;

3: use ieee.numeric std.all;

4: entity cnt5 is

5:

port(

6:

clk, reset, en: in std logic;

7:

Q: out std logic vector(4 downto 0)

8:

);

9: end cnt5;

10: architecture arch of cnt5 is

signal count : unsigned(4 downto 0);

11:

12:

begin

13:

process(clk,reset)

14:

begin

15:

if(reset='1') then

count <= "00000";

16:

17:

elsif(rising edge(clk) and (en='1')) then

18:

count <= count + "00001";

19:

end if;

20:

end process;

21:

Q <= std logic vector(count(4 downto 0));

22: end arch;

```