## Prova d'esame di RETI LOGICHE (Prof. E. Torti)

## Lauree in Ing. Elettronica e Informatica DM 270 23 settembre 2025

## CANDIDATO: n. matricola:

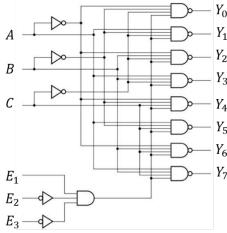

1) Si ricavino, in un'opportuna forma, la tabella di verità e le equazioni booleane del seguente circuito, descrivendo con chiarezza la sua funzione.

- 2) Si realizzi un circuito logico in grado di realizzare una diversa operazione matematica in funzione del valore di un ingresso di selezione S. Quando S vale 0, l'operazione da effettuare deve essere 9A, mentre quando S vale 1 l'operazione deve essere 7A. Si supponga che il valore di A sia rappresentato su 5 bit. Quale codifica deve essere adottata? Si indichi, motivando adeguatamente la risposta, Il ritardo totale del circuito supponendo che ogni porta logica abbia un tempo di propagazione pari a 2 ns.

- 3) Si discutano i diversi parametri tecnologici che caratterizzano le diverse porte logiche, evidenziando il loro impatto sulla realizzazione di un circuito complesso.

- 4) Si progetti un circuito sequenziale che rispetti le seguenti specifiche. Il circuito ha un ingresso X e due uscite Y e Z. Inizialmente, il circuito si trova in modalità riconoscimento di sequenza e deve riconoscere la sequenza 1011 applicata all'ingresso X. In questa fase, l'uscita Y varrà 1 solo quando negli istanti precedenti sono stati applicati all'ingresso X i valori 101 ed il valore attuale dell'ingresso X è 1. In tutti gli altri casi il valore di Y è pari a 0. Dopo aver riconosciuto la sequenza, il circuito entra in modalità generazione e ripete la sequenza appena riconosciuta sull'uscita Z, indipendentemente dal valore assunto da X. In tutti gli altri casi Z sarà pari a 0. Dopo la generazione dell'ultimo bit della sequenza di uscita, il circuito dovrà rientrare in modalità riconoscimento di sequenza, permettendo il riconoscimento di sequenze concatenate rispetto all'ultimo bit inserito durante la fase di riconoscimento. Si adotti un'opportuna codifica, motivando la risposta, e si ricavino le equazioni booleane del circuito. Si motivi inoltre la scelta del formalismo utilizzato per ciascuna delle due uscite. Calcolare infine il costo totale del circuito assumendo che il costo di un singolo flip-flop sia pari a 14.

- 5) Si progetti un contatore a costo minimo da -2 a 5 su un numero minimo di bit, utilizzando solo flip-flop JK. Il contatore dovrà inoltre essere dotato di un'uscita Z che indichi la presenza del valore 0 all'interno del contatore. Si disegni il diagramma di stato, indicando cosa accadrebbe qualora si presentassero in uscita degli stati diversi rispetto a quelli considerati dalle

- specifiche. Calcolare infine il costo totale del circuito, assumendo che il costo di un singolo flip-flop sia pari a 14.

- 6) Si discutano le diverse tipologie di contatori binari, evidenziando per ciascuna di esse i vantaggi e gli svantaggi e gli ambiti applicativi.

- 7) Si consideri il seguente codice VHDL che descrive uno shift register a 5 bit. Commentare sinteticamente gli statement del codice (riportare sul foglio il numero della riga seguito dal relativo commento) indicando quale tipo di descrizione è stata utilizzata. Spiegare poi come dovrebbe essere modificato il codice per includere una porta di enable attiva bassa. Modificare poi il codice per aggiungere una porta OP che permetta di scegliere fra due operazioni: se OP=0 viene effettuato lo shift, altrimenti il valore memorizzato all'interno del registro viene incrementato di 1. Infine, si introduca una porta che indichi la presenza di un multiplo di 4 all'interno del registro.

```

1: library ieee;

2: use ieee.std logic 1164.all;

3: entity sr5 is

4:

port(

5:

clk, reset, si : in std logic;

6:

Q: out std logic vector(4 downto 0);

so: out std logic

7:

8:

);

9: end sr5;

10: architecture arch of sr5 is

11:

signal shift: std logic vector(4 downto 0);

12:

begin

13:

process(clk,reset)

14:

begin

15:

if(reset='1') then

shift <= "00000";

16:

17:

elsif(rising edge(clk)) then

shift <= shift(3 downto 0) & si;

18:

19:

end if:

20:

end process;

21:

O \le shift;

22:

so \le shift(4);

23: end arch;

```